Selective Software-Implemented Hardware Fault Tolerance Techniques to Detect Soft Errors in Processors with Reduced Overhead

**Eduardo Chielle**

# Tesis Doctorales UNIVERSIDAD de ALICANTE

www.eltallerdigital.com

### Selective Software-Implemented Hardware Fault Tolerance Techniques to Detect Soft Errors in Processors with Reduced Overhead

# Eduardo Chielle

**Tesis doctoral** Alicante, abril 2016

DEPARTAMENTO DE TECNOLOGÍA INFORMÁTICA Y COMPUTACIÓN

Tesis en contutela con la UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL (UFRGS)

### Selective Software-Implemented Hardware Fault Tolerance Techniques to Detect Soft Errors in Processors with Reduced Overhead

Eduardo Chielle

Tesis presentada para aspirar al grado de DOCTOR POR LA UNIVERSIDAD DE ALICANTE PROGRAMA DE DOCTORADO EN INFORMÁTICA

> Directores Dr. Sergio Cuenca-Asensi Dra. Fernanda Lima Kastensmidt

> > ABRIL 2016

### CONTENTS

|                                                                                                                                     | 9                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| LIST OF FIGURES                                                                                                                     | 11                                                                                                   |

| LIST OF TABLES                                                                                                                      | 19                                                                                                   |

| PREFACE                                                                                                                             | 21                                                                                                   |

| ABSTRACT                                                                                                                            | 23                                                                                                   |

| RESUMO                                                                                                                              | 25                                                                                                   |

| RESUMEN                                                                                                                             | 27                                                                                                   |

| 1 INTRODUCTION                                                                                                                      |                                                                                                      |

| 1.1 Motivation                                                                                                                      | .29                                                                                                  |

| 1.2 Objectives and contributions                                                                                                    | .31                                                                                                  |

|                                                                                                                                     | 22                                                                                                   |

| 1.3 Thesis organization                                                                                                             | .34                                                                                                  |

| 2 DEFINITIONS AND BACKGROUND KNOWLEDGE                                                                                              |                                                                                                      |

| 2 DEFINITIONS AND BACKGROUND KNOWLEDGE                                                                                              | <b>33</b><br>.33                                                                                     |

| 2 DEFINITIONS AND BACKGROUND KNOWLEDGE         2.1 Sources of ionizing radiation.         2.2 Non-destructive Single Event Effects. | <b>33</b><br>.33<br>.34                                                                              |

| 2 DEFINITIONS AND BACKGROUND KNOWLEDGE                                                                                              | <b>33</b><br>.33<br>.34                                                                              |

| 2 DEFINITIONS AND BACKGROUND KNOWLEDGE         2.1 Sources of ionizing radiation.         2.2 Non-destructive Single Event Effects. | <b>33</b><br>.33<br>.34<br>.35                                                                       |

| 2 DEFINITIONS AND BACKGROUND KNOWLEDGE                                                                                              | <b>33</b><br>.33<br>.34<br>.35<br>.35<br>.36<br>.38<br>.38                                           |

| 2 DEFINITIONS AND BACKGROUND KNOWLEDGE                                                                                              | <ul> <li>33</li> <li>.33</li> <li>.34</li> <li>.35</li> <li>.36</li> <li>.38</li> <li>.39</li> </ul> |

| 3.2 Con          | trol-flow techniques                                        | 45                                      |

|------------------|-------------------------------------------------------------|-----------------------------------------|

| 3.2.1            | CCA                                                         | 45                                      |

| 3.2.2            | ECCA                                                        |                                         |

| 3.2.3            | CFCSS                                                       |                                         |

| 3.2.4            | YACCA                                                       |                                         |

| 3.2.5            | CEDA                                                        | 50                                      |

| 3.2.6            | HETA                                                        |                                         |

| 3.2.7            | Drawbacks of control-flow techniques                        | 53                                      |

|                  |                                                             |                                         |

|                  | bined data-flow and control-flow techniques                 |                                         |

| 3.3.1            | Transformation rules by Rebaudengo                          |                                         |

| 3.3.2            | Transformation rules by Nicolescu                           |                                         |

| 3.3.3            | SWIFT                                                       |                                         |

| 3.3.4            | Transformation rules by Azambuja                            |                                         |

| 3.3.5            | Drawbacks of combined data-flow and control-flow techniques | 64                                      |

|                  |                                                             |                                         |

|                  | ctive hardening                                             |                                         |

| 3.4.1            | Selective SWIFT-R                                           | 64                                      |

|                  |                                                             |                                         |

| 4 METH           | ODOLOGIES AND METRICS                                       | 69                                      |

| -                |                                                             |                                         |

| 4.1 Har          | dening methodology                                          | 60                                      |

| <b>4.1</b> 11a1  | aching incluouology                                         |                                         |

| 4.2 Faul         | It injection methodology                                    | 70                                      |

| 4.2.1            | Fault injection by logical simulation                       |                                         |

| 4.2.2            | Radiation tests with neutrons and heavy ions                |                                         |

|                  |                                                             |                                         |

| 4.3 Met          | rics                                                        | 72                                      |

| <b>4.</b> 5 Micu | 11C5                                                        | ••••••••••••••••••••••••••••••••••••••• |

|                  |                                                             |                                         |

| 5 PROF           | POSED TECHNIQUES                                            | 75                                      |

|                  |                                                             |                                         |

| 5.1 Data         | a-flow techniques based on rules                            |                                         |

| 5.1.1            | Methodology and implementation                              |                                         |

| 5.1.2            | Fault injection results in the miniMIPS processor           | 80                                      |

|                  |                                                             |                                         |

| 5.2 Con          | trol-flow technique                                         |                                         |

| 5.2.1            | Methodology and implementation                              |                                         |

| 5.2.2            | Fault injection results in the miniMIPS processor           | 90                                      |

|                  |                                                             |                                         |

| 5.3 Con          | bined data-flow and control-flow techniques                 | 92                                      |

| 5.3.1            | Methodology and implementation                              |                                         |

| 5.3.2            | Fault injection results in the miniMIPS processor           |                                         |

| 5.3.3            | Radiation test results in the ARM Cortex-A9 processor       |                                         |

|                  | Test with neutrons                                          |                                         |

| 5.3.3.2          | 2 Test with heavy ions                                      | 101                                     |

|                  |                                                             |                                         |

| 5.4 Sum          | mary                                                        | 104                                     |

|                  |                                                             |                                         |

| 6 PROF           | POSED SELECTIVE HARDENING                                   | 105                                     |

| 5 1101           |                                                             |                                         |

| 6.1 Sele         | ctive data-flow technique                                   | 105                                     |

| 6.1.1            | Methodology and implementation                              |                                         |

| 6.1.2            | Fault injection results in the miniMIPS processor           |                                         |

| 0.1.2            | r aux injection results in the minimum o processor          | 107                                     |

| 6.2 Sele         | ctive control-flow technique                                | 115                                     |

| 6.2.1            | Methodology and implementation                              |                                         |

| 0.2.1            | niemodology und implementation                              |                                         |

| 6.2.2 Fault injection results                                                                                                                                                                                                                                                                                               | s in the miniMIPS processor117                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 6.3 Selective data-flow techni                                                                                                                                                                                                                                                                                              | ique and selective control-flow technique142                                            |

|                                                                                                                                                                                                                                                                                                                             | plementation                                                                            |

|                                                                                                                                                                                                                                                                                                                             | s in the miniMIPS processor                                                             |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 6.3.4 Reducing number of                                                                                                                                                                                                                                                                                                    | points for fitting model164                                                             |

| 6.4 Summary                                                                                                                                                                                                                                                                                                                 |                                                                                         |

| 7 CONCLUDING REMA                                                                                                                                                                                                                                                                                                           | RKS181                                                                                  |

| 7.1 Conclusions                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 7.2 Future work                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 7.3 Publications                                                                                                                                                                                                                                                                                                            |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| 7.3.3 Conferences                                                                                                                                                                                                                                                                                                           |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| REFERENCES                                                                                                                                                                                                                                                                                                                  |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| <b>APPENDIX A <cft-tooi< b=""></cft-tooi<></b>                                                                                                                                                                                                                                                                              |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

| A.1 Configuration                                                                                                                                                                                                                                                                                                           |                                                                                         |

| A.2 Parameters                                                                                                                                                                                                                                                                                                              |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             | >                                                                                       |

|                                                                                                                                                                                                                                                                                                                             | Sitat u Alacant                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

|                                                                                                                                                                                                                                                                                                                             |                                                                                         |

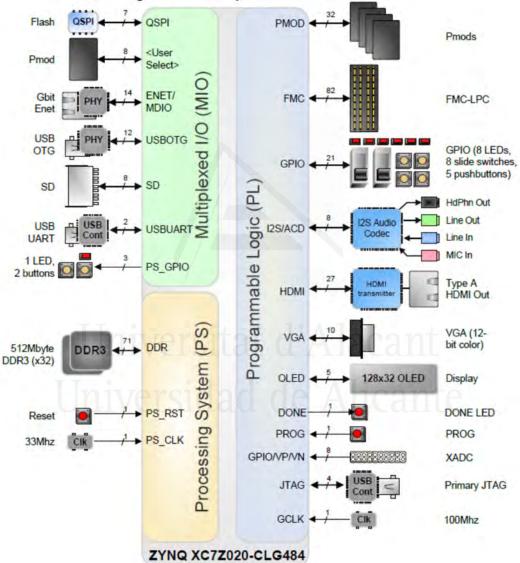

| B.2 ARM Cortex-A9                                                                                                                                                                                                                                                                                                           | 197<br>Indiad die Alicantic 198                                                         |

| B.2 ARM Cortex-A9                                                                                                                                                                                                                                                                                                           |                                                                                         |

| B.2ARM Cortex-A9B.3ZedBoard                                                                                                                                                                                                                                                                                                 | 197<br>Indiad die Alicantic 198                                                         |

| B.2ARM Cortex-A9B.3ZedBoardAPPENDIX C <benchma< td=""></benchma<>                                                                                                                                                                                                                                                           | 197<br>198<br>198<br>199<br>ARKS>                                                       |

| B.2ARM Cortex-A9B.3ZedBoardAPPENDIX C <benchma< th="">C.1Bubble sort</benchma<>                                                                                                                                                                                                                                             | 197<br>198<br>198<br>199<br>ARKS>                                                       |

| <ul> <li>B.2 ARM Cortex-A9</li> <li>B.3 ZedBoard</li> <li>APPENDIX C <benchma< li=""> <li>C.1 Bubble sort</li> <li>C.2 Dijkstra's algorithm</li> </benchma<></li></ul>                                                                                                                                                      | 197<br>198<br>198<br>199<br>ARKS>                                                       |

| <ul> <li>B.2 ARM Cortex-A9</li> <li>B.3 ZedBoard</li> <li>APPENDIX C <benchma< li=""> <li>C.1 Bubble sort</li> <li>C.2 Dijkstra's algorithm</li> </benchma<></li></ul>                                                                                                                                                      | 197<br>198<br>198<br>199<br>ARKS>                                                       |

| <ul> <li>B.2 ARM Cortex-A9</li> <li>B.3 ZedBoard</li> <li>APPENDIX C <benchma< li=""> <li>C.1 Bubble sort</li> <li>C.2 Dijkstra's algorithm</li> <li>C.3 Recursive depth-first sear</li> </benchma<></li></ul>                                                                                                              | 197<br>198<br>198<br>199<br>ARKS>                                                       |

| <ul> <li>B.2 ARM Cortex-A9</li> <li>B.3 ZedBoard</li> <li>APPENDIX C <benchma< li=""> <li>C.1 Bubble sort</li> <li>C.2 Dijkstra's algorithm</li> <li>C.3 Recursive depth-first sear</li> <li>C.4 Sequential depth-first sea</li> </benchma<></li></ul>                                                                      | 197<br>198<br>198<br>199<br>ARKS> 201<br>203<br>206<br>rch 208                          |

| <ul> <li>B.2 ARM Cortex-A9</li> <li>B.3 ZedBoard</li> <li>APPENDIX C <benchma< li=""> <li>C.1 Bubble sort</li> <li>C.2 Dijkstra's algorithm</li> <li>C.3 Recursive depth-first sear</li> <li>C.4 Sequential depth-first sea</li> <li>C.5 Matrix multiplication</li> </benchma<></li></ul>                                   | 197<br>198<br>199<br>ARKS> 201<br>203<br>206<br>rch 208<br>rch 209                      |

| <ul> <li>B.2 ARM Cortex-A9</li> <li>B.3 ZedBoard</li> <li>APPENDIX C <benchma< li=""> <li>C.1 Bubble sort</li> <li>C.2 Dijkstra's algorithm</li> <li>C.3 Recursive depth-first sear</li> <li>C.4 Sequential depth-first sear</li> <li>C.5 Matrix multiplication</li> <li>C.6 Run length encoding</li> </benchma<></li></ul> | 197<br>198<br>198<br>199<br>ARKS> 201<br>203<br>203<br>206<br>rch 208<br>rch 209<br>211 |

| <b>C.9</b> | Tower of Hanoi           |     |

|------------|--------------------------|-----|

| RES        | SUMEN DE LA TESIS        | 221 |

| <b>D.1</b> | Introducción             |     |

| <b>D.2</b> | Metodología y resultados |     |

| <b>D.3</b> | Conclusiones             |     |

### LIST OF ABBREVIATIONS AND ACRONYMS

| BID       | Basic Block Identifier                                   |

|-----------|----------------------------------------------------------|

| BS        | Bubble Sort                                              |

| CCA       | Control Flow Checking using Assertions                   |

| CEDA      | Control flow Error Detection through Assertions          |

| CFCSS     | Control Flow Checking by Software Signatures             |

| CFID      | Control Flow Identifier                                  |

| CFT       | Configurable Fault Tolerant                              |

| DA        | Dijkstra's Algorithm                                     |

| ECCA      | Enhanced Control Flow Checking using Assertions          |

| EDDI      | Error Detection by Duplicated Instructions               |

| HETA      | Hybrid Error-Detection Technique Using Assertions        |

| MM        | Matrix Multiplication                                    |

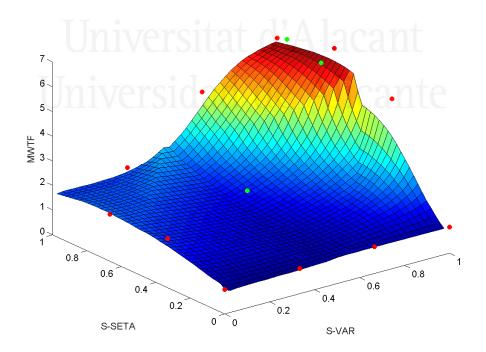

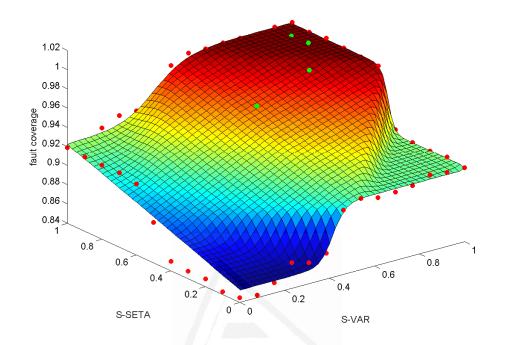

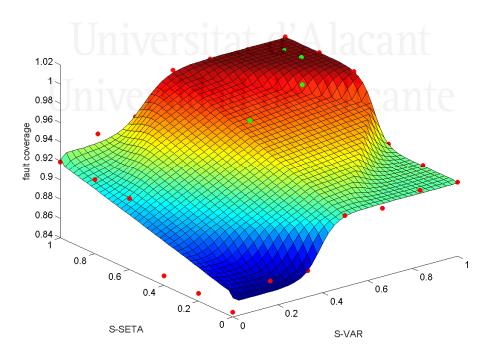

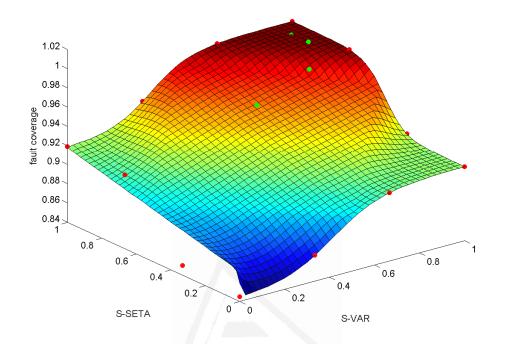

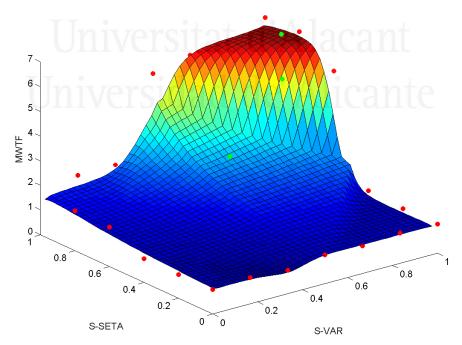

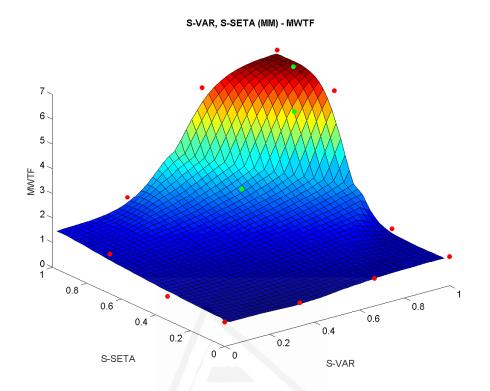

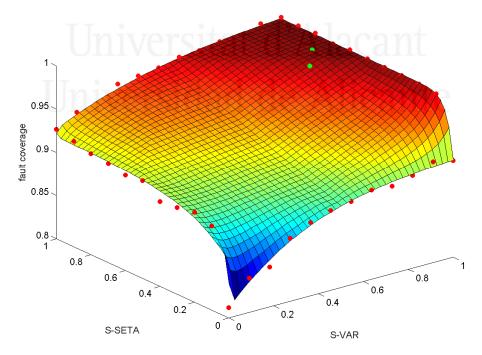

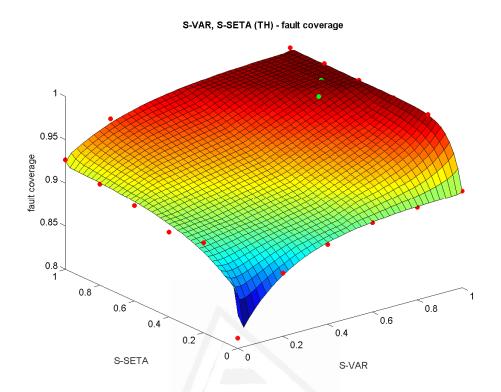

| MWTF      | Mean Work To Failure                                     |

| PC        | Program Counter                                          |

| rDFS      | Recursive Depth-First Search                             |

| RLE       | Run-Length Encoding                                      |

| RISC      | Reduced Instruction Set Computer                         |

| RTL       | Register Transfer Level                                  |

| sDFS      | Sequential Depth-First Search                            |

| SEE       | Single Events Effects                                    |

| SET       | Single Event Transient                                   |

| SETA      | Software-only Error-detection Technique using Assertions |

| SEU       | Single Event Upset                                       |

| SIHFT     | Software-Implemented Hardware Fault Tolerance            |

| SUM       | Summation                                                |

| SWIFT     | Software Implemented Fault Tolerance                     |

| SWIFT-R   | SWIFT - Recovery                                         |

| S-SETA    | Selective SETA                                           |

| S-SWIFT-R | Selective SWIFT-R                                        |

| S-VAR     | Selective VAR                                            |

| TEA2      | TETRA Encryption Algorithm 2                             |

| Terrestrial Trunked Radio                          |

|----------------------------------------------------|

| Tower of Hanoi                                     |

| Variables                                          |

| VHSIC Hardware Description Language                |

| Very High Speed Integrated Circuit                 |

| Yet Another Control-Flow Checking using Assertions |

|                                                    |

### **LIST OF FIGURES**

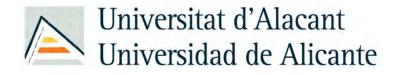

| Fig. 2.1: Source of ionizing radiation                                                                 | 33   |

|--------------------------------------------------------------------------------------------------------|------|

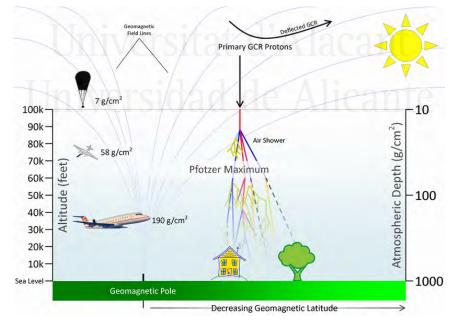

| Fig. 2.2: SEU and SET in circuits.                                                                     |      |

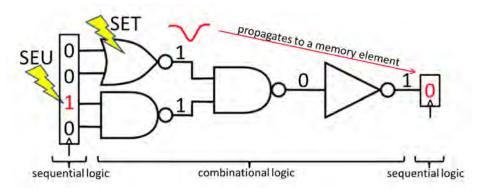

| Fig. 2.3: Effect of soft errors in processors.                                                         | 35   |

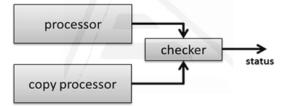

| Fig. 2.4: Example of DWC hardware-based technique using a black box processors                         |      |

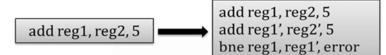

| Fig. 2.5: Example of a SIHFT technique.                                                                |      |

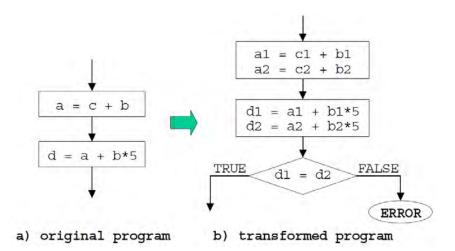

| Fig. 2.6: Example of a data-flow technique                                                             |      |

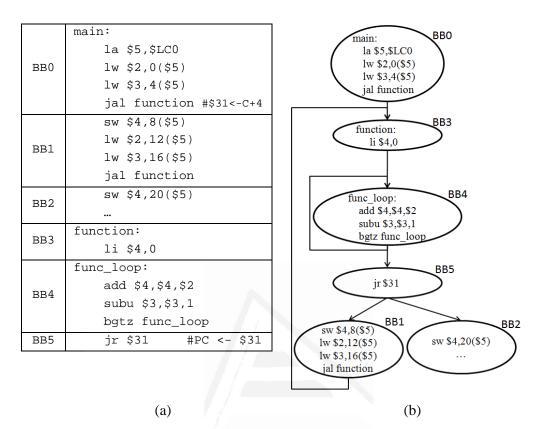

| Fig. 2.7: Basic Blocks and program flow                                                                |      |

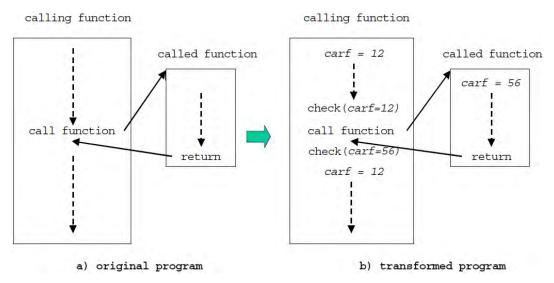

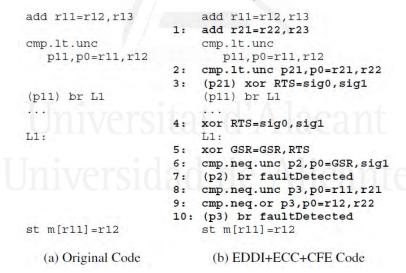

| Fig. 3.1: EDDI technique (REIS, 2005b).                                                                |      |

| Fig. 3.2: VAR1 technique (AZAMBUJA, 2011a).                                                            |      |

| Fig. 3.3: VAR2 technique (AZAMBUJA, 2011a).                                                            | 44   |

| Fig. 3.4: VAR3 technique (AZAMBUJA, 2011a).                                                            | 44   |

| Fig. 3.5: Example of CCA technique (ALKHALIFA, 1999).                                                  | 46   |

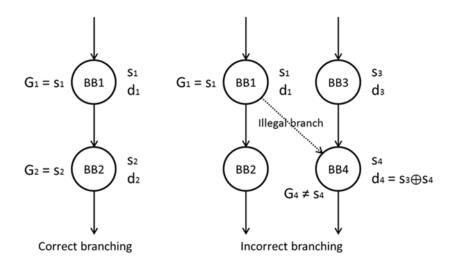

| Fig. 3.6: Signature update during correct and illegal branch.                                          | 48   |

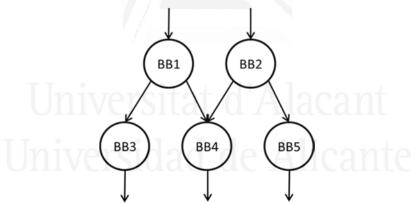

| Fig. 3.7: Basic blocks sharing a common successor.                                                     | 48   |

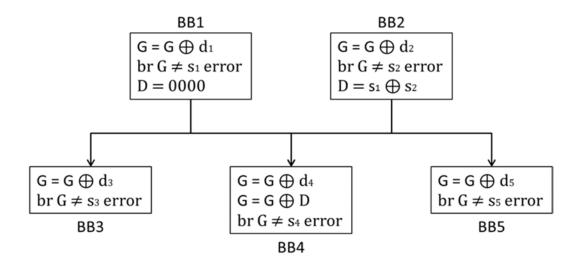

| Fig. 3.8: Update of D when BBs share a successor                                                       |      |

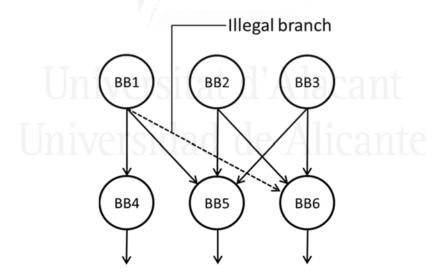

| Fig. 3.9: Undetected illegal branch.                                                                   | 49   |

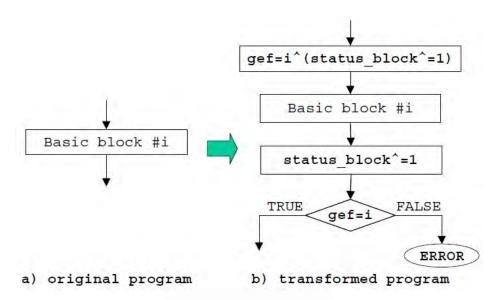

| Fig. 3.10: Transformation rules by Rebaudengo to protect the data                                      |      |

| Fig. 3.11: Transformation rules by Rebaudengo to protect the data in procedures                        | 55   |

| Fig. 3.12: Transformation rules by Rebaudengo to protect the control-flow.                             |      |

| Fig. 3.13: Transformation rules by Rebaudengo to protect branch decisions                              | 56   |

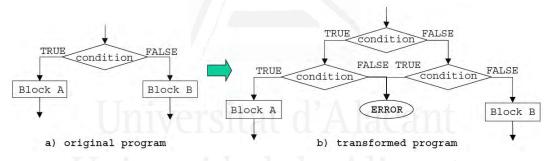

| Fig. 3.14: Transformation rules by Rebaudengo to protect the control in procedures                     | 56   |

| Fig. 3.15: Transformation rules to protect the data (NICOLESCU, 2003).                                 | 58   |

| Fig. 3.16: Transformation rules to protect the control-flow (NICOLESCU, 2003)                          | 59   |

| Fig. 3.17: Transformation to protect branch decisions (NICOLESCU, 2003)                                | 59   |

| Fig. 3.18: Transformation rules to protect procedures (NICOLESCU, 2003)                                | 60   |

| Fig. 3.19: Transformation rules (REIS, 2005b).                                                         | 61   |

| Fig. 3.20: Example of the modified CCA proposed by (AZAMBUJA, 2011b)                                   | 63   |

| Fig. 3.21: Technique to detect illegal branches inside basic blocks by (AZAMBUJA, 2011b)               |      |

| Fig. 3.22: Example of a code hardened by S-SWIFT-R (RESTREPO-CALLE, 2016)                              | 65   |

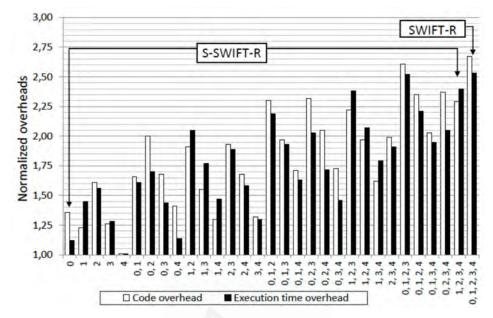

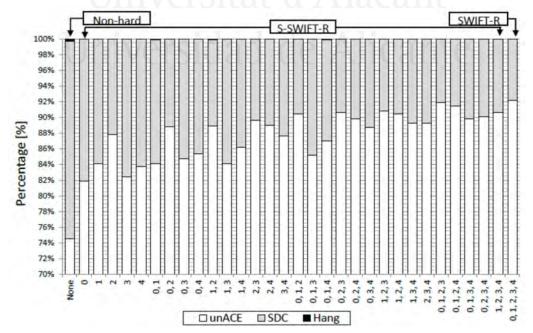

| Fig. 3.23: Code size and execution time overheads for an FIR hardened by S-SWIFT-R (RESTREPO-          |      |

| CALLE, 2016)                                                                                           |      |

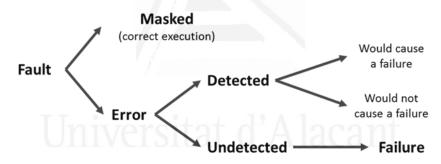

| Fig. 4.1: Fault, error, and failure in processors hardened by SIHFT techniques                         |      |

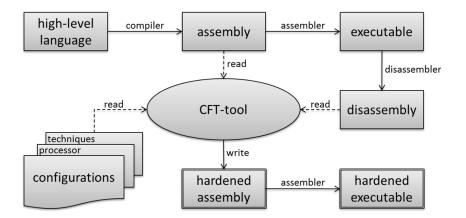

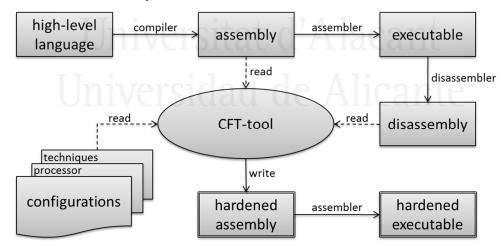

| Fig. 4.2: Steps to protect an application using CFT-tool                                               | 70   |

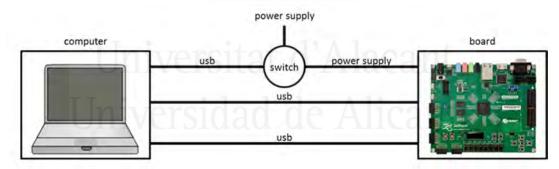

| Fig. 4.3: Setup for radiation tests                                                                    | 71   |

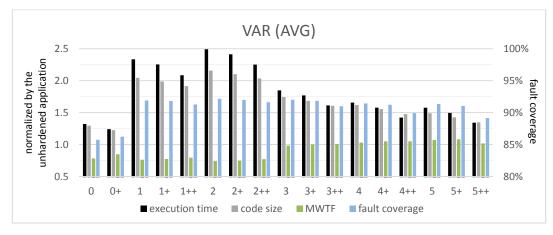

| Fig. 5.1: Average results for the VAR techniques. The execution time, code size, and MWTF are          |      |

| normalized by the unhardened applications (left axis). The fault coverage is presented in percentage   |      |

| (right axis)                                                                                           |      |

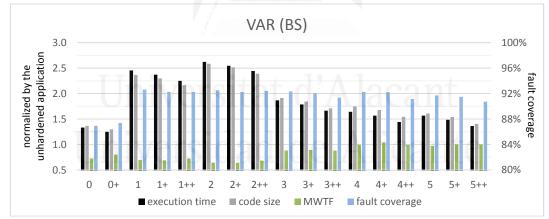

| Fig. 5.2: Results for the bubble sort (BS) hardened by the VAR techniques. The execution time, code s  |      |

| and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented     |      |

| percentage (right axis)                                                                                |      |

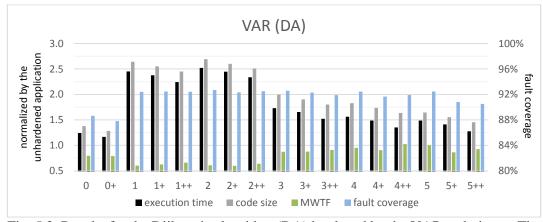

| Fig. 5.3: Results for the Dijkstra's algorithm (DA) hardened by the VAR techniques. The execution time |      |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is    |      |

| presented in percentage (right axis)                                                                   | 82   |

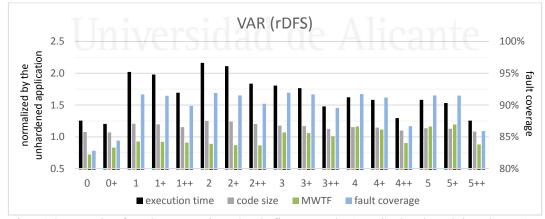

| Fig. 5.4: Results for the recursive depth-first search (rDFS) hardened by the VAR techniques. The      |      |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fa   |      |

| coverage is presented in percentage (right axis).                                                      | 82   |

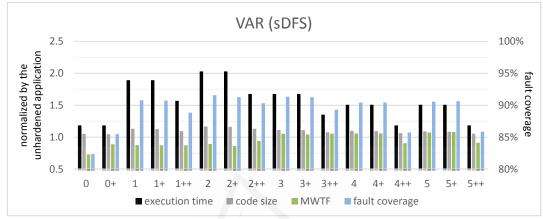

| Fig. 5.5: Results for the sequential depth-first search (sDFS) hardened by the VAR techniques. The     |      |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The for  |      |

| coverage is presented in percentage (right axis).                                                      |      |

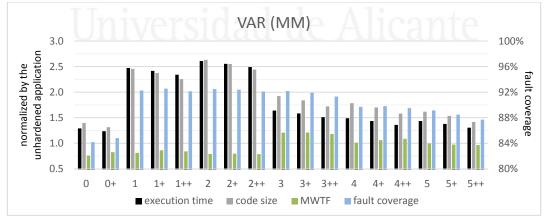

| Fig. 5.6: Results for the matrix multiplication (MM) hardened by the VAR techniques. The execution t   | ime, |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is    | ~ -  |

| presented in percentage (right axis)                                                                   | 83   |

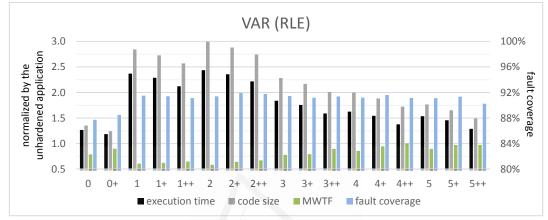

| Fig. 5.7: Results for the run length encoding (RLE) hardened by the VAR techniques. The execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| presented in percentage (right axis)84                                                                                                                                                                      |

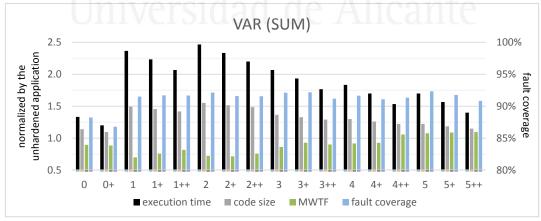

| Fig. 5.8: Results for the summation (SUM) hardened by the VAR techniques. The execution time, code                                                                                                          |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                                                                              |

| presented in percentage (right axis)                                                                                                                                                                        |

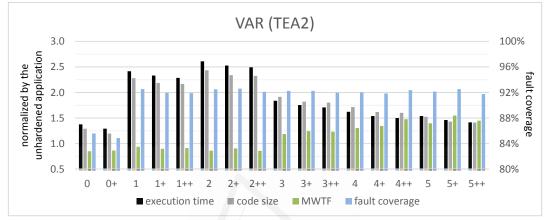

| Fig. 5.9: Results for the TETRA encryption algorithm (TEA2) hardened by the VAR techniques. The execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault     |

| coverage is presented in percentage (right axis)85                                                                                                                                                          |

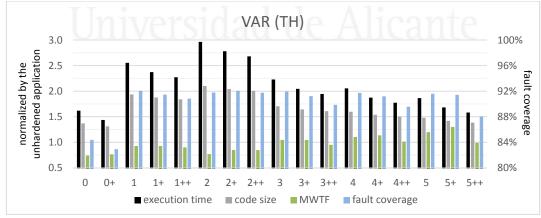

| Fig. 5.10: Results for the Tower of Hanoi (TH) hardened by the VAR techniques. The execution time,                                                                                                          |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                                                                         |

| presented in percentage (right axis)85                                                                                                                                                                      |

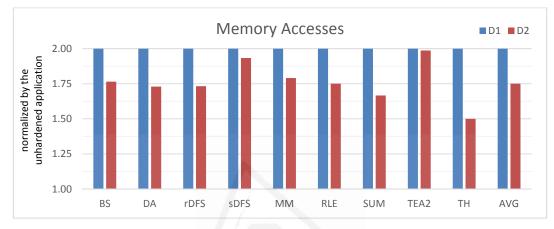

| Fig. 5.11: Memory accesses for duplication rules D1 and D2 for the nine case-study applications and                                                                                                         |

| average (harmonic mean)                                                                                                                                                                                     |

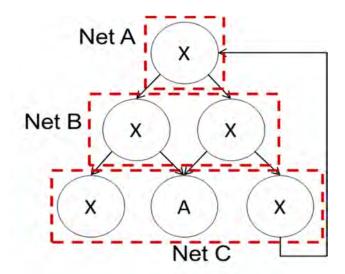

| Fig. 5.12: Representation of a program flow. Basic blocks (circles) classified as of type A or X, and                                                                                                       |

| grouped into networks (dashed rectangles). The arrows indicate the valid directions that a basic block can take                                                                                             |

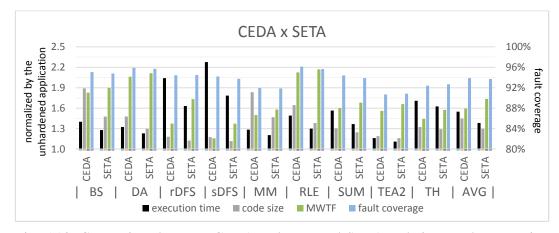

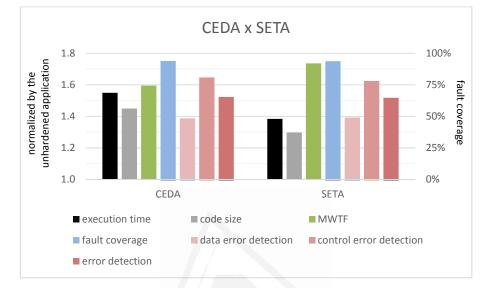

| Fig. 5.10: Comparison between CEDA and proposed SETA techniques. The execution time, code size,                                                                                                             |

| and MWTF are presented normalized by the unhardened application (left axis). The fault coverage is                                                                                                          |

| presented in percentage (right axis)91                                                                                                                                                                      |

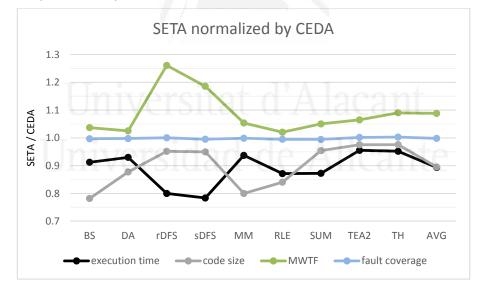

| Fig. 5.11: Comparison between SETA and CEDA. The results obtained with SETA are normalized by the                                                                                                           |

| ones obtained with CEDA                                                                                                                                                                                     |

| Fig. 5.12: Comparison between CEDA and SETA. The average results are presented. The execution time,                                                                                                         |

| code size, and MWTF are normalized by the unhardened applications (left axis). The fault coverage and                                                                                                       |

| error detection rates are presented in percentage (right axis)92                                                                                                                                            |

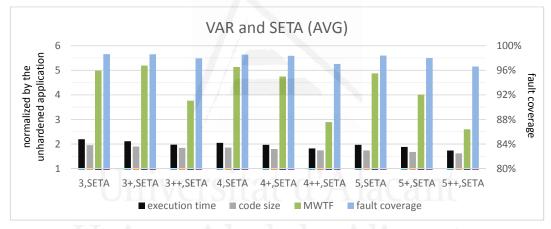

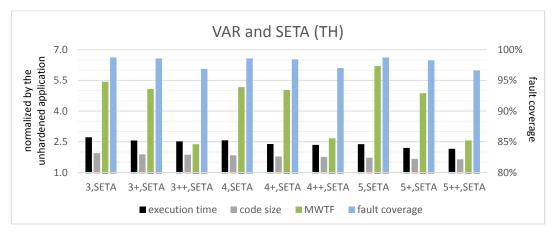

| Fig. 5.13: Average results for combining VAR and SETA. The execution time, code size, and MWTF are                                                                                                          |

| normalized by the unhardened application (left axis). The fault coverage is presented in percentage (right                                                                                                  |

| axis)94                                                                                                                                                                                                     |

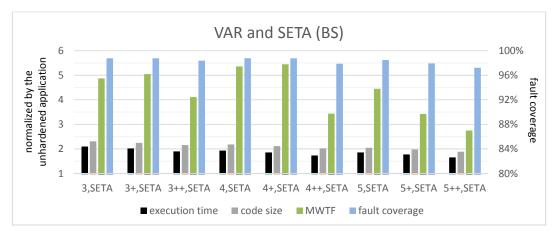

| Fig. 5.14: Results of combining VAR and SETA for the bubble sort (BS). The execution time, code size,                                                                                                       |

| and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented in                                                                                                       |

| percentage (right axis)                                                                                                                                                                                     |

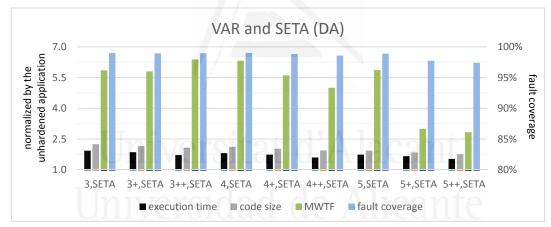

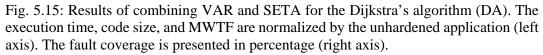

| Fig. 5.15: Results of combining VAR and SETA for the Dijkstra's algorithm (DA). The execution time,                                                                                                         |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                                                                         |

| presented in percentage (right axis)95                                                                                                                                                                      |

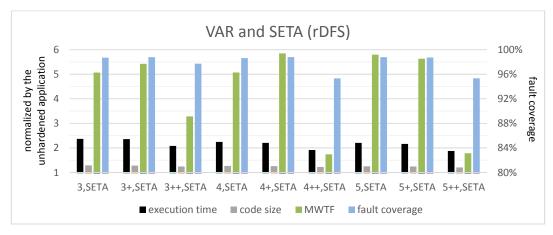

| Fig. 5.16: Results of combining VAR and SETA for the recursive depth-first search (rDFS). The execution                                                                                                     |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage                                                                                                      |

| is presented in percentage (right axis)96                                                                                                                                                                   |

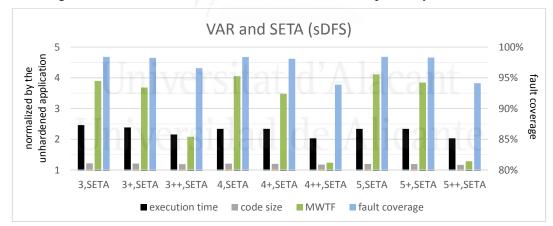

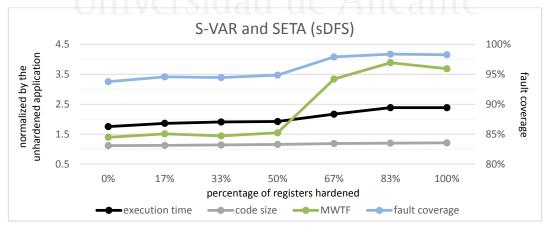

| Fig. 5.17: Results of combining VAR and SETA for the sequential depth-first search (sDFS). The                                                                                                              |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault                                                                                                     |

| coverage is presented in percentage (right axis)96                                                                                                                                                          |

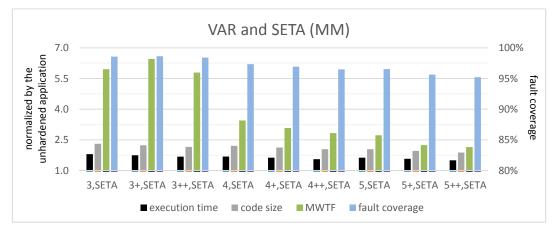

| Fig. 5.18: Results of combining VAR and SETA for the matrix multiplication (MM). The execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is    |

| presented in percentage (right axis)                                                                                                                                                                        |

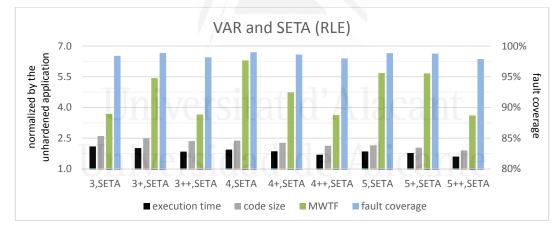

| Fig. 5.19: Results of combining VAR and SETA for the run-length encoding (RLE). The execution time,                                                                                                         |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                                                                         |

| presented in percentage (right axis)                                                                                                                                                                        |

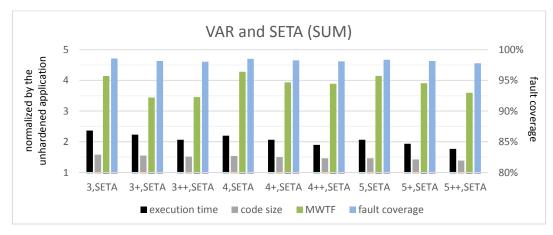

| Fig. 5.20: Results of combining VAR and SETA for the summation (SUM). The execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented in  |

| percentage (right axis)                                                                                                                                                                                     |

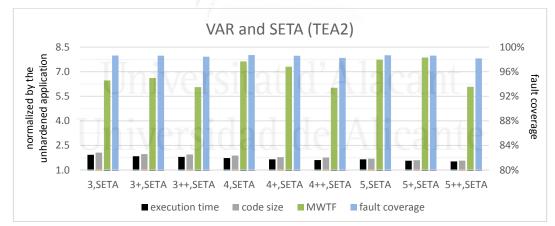

| Fig. 5.21: Results of combining VAR and SETA for the TETRA encryption algorithm (TEA2). The                                                                                                                 |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault                                                                                                     |

| coverage is presented in percentage (right axis)                                                                                                                                                            |

| Fig. 5.22: Results of combining VAR and SETA for the Tower of Hanoi (TH). The execution time, code                                                                                                          |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                                                                              |

| presented in percentage (right axis)                                                                                                                                                                        |

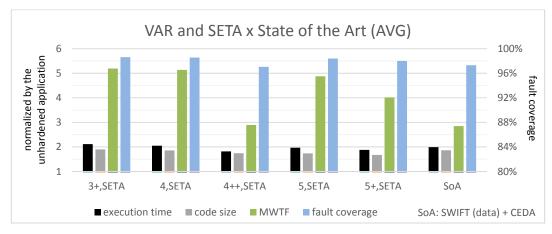

| Fig. 5.23: Average results for combining VAR and SETA vs. state-of-the-art (SoA) techniques. The                                                                                                            |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented in percentage (right axis)                                                    |

|                                                                                                                                                                                                             |

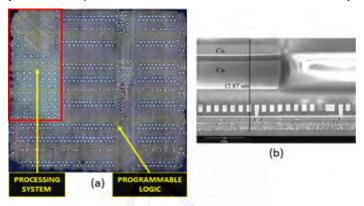

| Fig. 5.24: (a) View of the surface of the XC7Z020-CLG484 device, and (b) Microscopic section of the XC7Z020-CLG484 device                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|

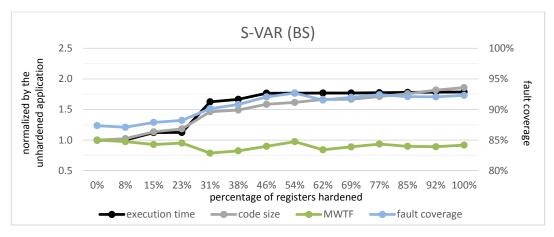

| Fig. 6.1: Results for the bubble sort (BS) hardened by the S-VAR technique. The execution time, code size,                                               |

| and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented in                                                    |

| percentage (right axis)                                                                                                                                  |

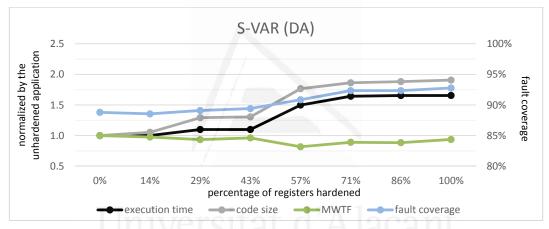

| Fig. 6.2: Results for the Dijkstra's algorithm (DA) hardened by the S-VAR technique. The execution time,                                                 |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                      |

| presented in percentage (right axis)                                                                                                                     |

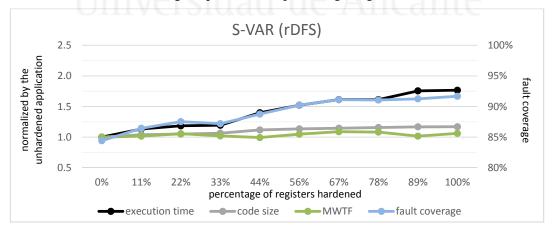

| Fig. 6.3: Results for the recursive depth-first search (rDFS) hardened by the S-VAR technique. The                                                       |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented in percentage (right axis) |

|                                                                                                                                                          |

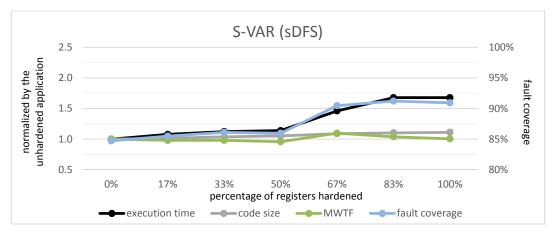

| Fig. 6.4: Results for the sequential depth-first search (sDFS) hardened by the S-VAR technique. The                                                      |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented in percentage (right axis) |

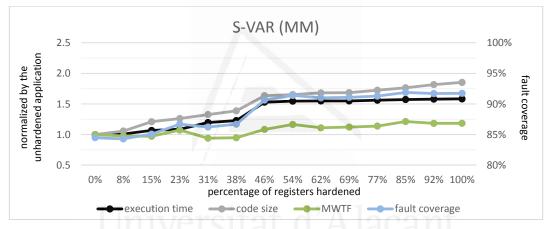

| Fig. 6.5: Results for the matrix multiplication (MM) hardened by the S-VAR technique. The execution                                                      |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage                                                   |

| is presented in percentage (right axis)                                                                                                                  |

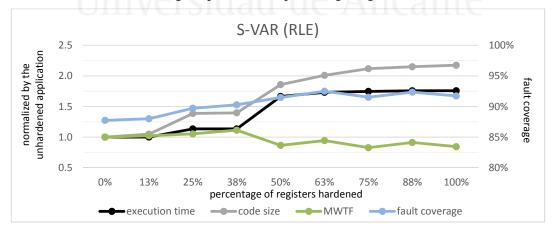

| Fig. 6.6: Results for the run length encoding (RLE) hardened by the S-VAR technique. The execution                                                       |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage                                                   |

| is presented in percentage (right axis)                                                                                                                  |

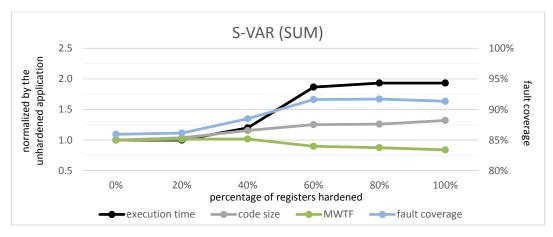

| Fig. 6.7: Results for the summation (SUM) hardened by the S-VAR technique. The execution time, code                                                      |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                           |

| presented in percentage (right axis)                                                                                                                     |

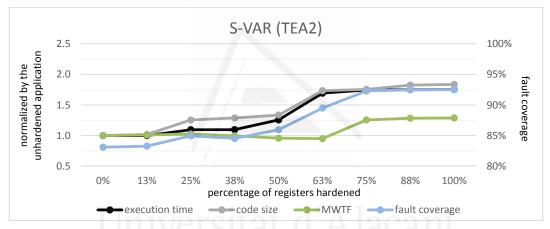

| Fig. 6.8: Results for the TETRA encryption algorithm (TEA2) hardened by the S-VAR technique. The                                                         |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault                                                  |

| coverage is presented in percentage (right axis)                                                                                                         |

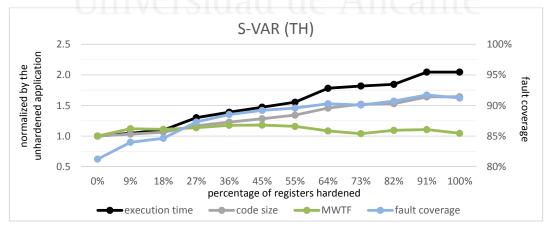

| Fig. 6.9: Results for the Tower of Hanoi (TH) hardened by the S-VAR technique. The execution time, code                                                  |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                           |

| presented in percentage (right axis)                                                                                                                     |

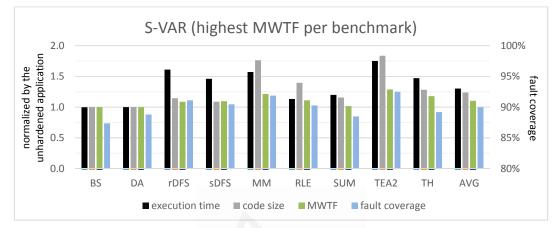

| Fig. 6.10: Highest MWTF for the benchmarks hardened by the S-VAR technique. The execution time,                                                          |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                      |

| presented in percentage (right axis)                                                                                                                     |

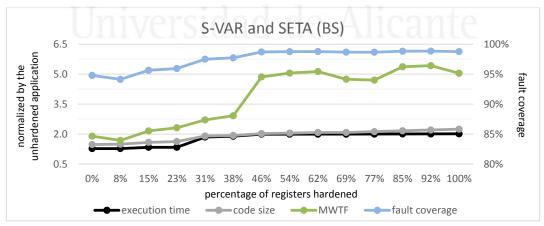

| Fig. 6.11: Results for the bubble sort (BS) hardened by S-VAR and SETA. The execution time, code size,                                                   |

| and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented in                                                    |

| percentage (right axis)                                                                                                                                  |

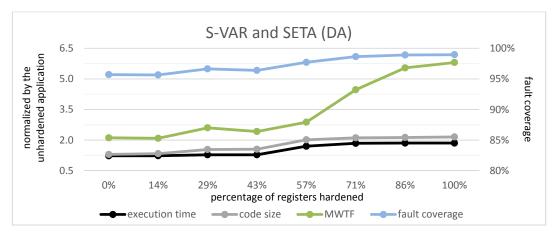

| Fig. 6.12: Results for the Dijkstra's algorithm (DA) hardened by S-VAR and SETA. The execution time,                                                     |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                      |

| presented in percentage (right axis)                                                                                                                     |

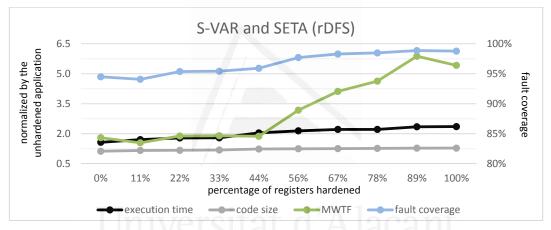

| Fig. 6.13: Results for the recursive depth-first search (rDFS) hardened by S-VAR and SETA. The                                                           |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault                                                  |

| coverage is presented in percentage (right axis)                                                                                                         |

| Fig. 6.14: Results for the sequential depth-first search (sDFS) hardened by S-VAR and SETA. The                                                          |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault                                                  |

| coverage is presented in percentage (right axis)                                                                                                         |

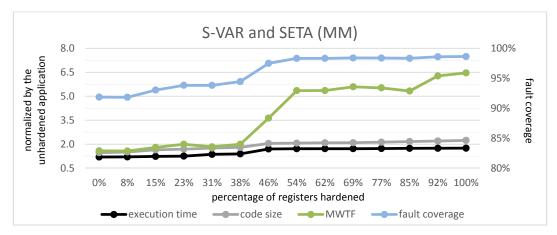

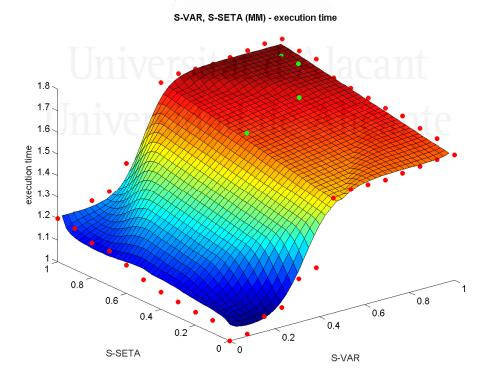

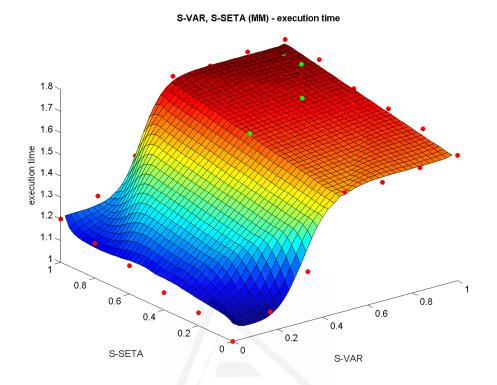

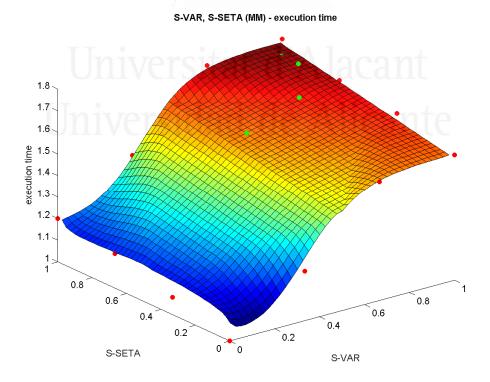

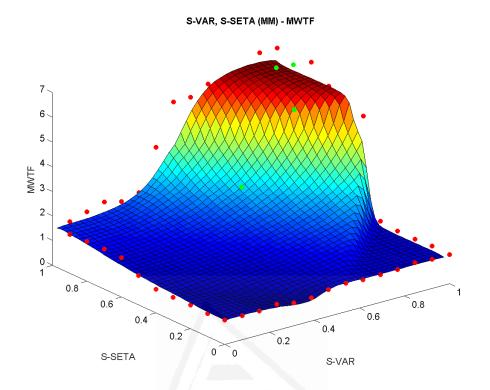

| Fig. 6.15: Results for the matrix multiplication (MM) hardened by S-VAR and SETA. The execution time,                                                    |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                      |

| presented in percentage (right axis)                                                                                                                     |

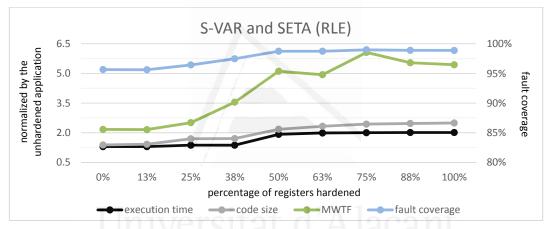

| Fig. 6.16: Results for the run length encoding (RLE) hardened by S-VAR and SETA. The execution time,                                                     |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                      |

| presented in percentage (right axis)113                                                                                                                  |

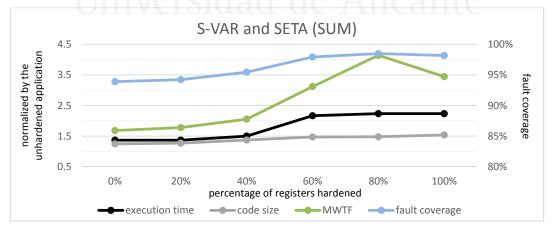

| Fig. 6.17: Results for the summation (SUM) hardened by S-VAR and SETA. The execution time, code size,                                                    |

| and MWTF are normalized by the unhardened application (left axis). The fault coverage is presented in                                                    |

| percentage (right axis)113                                                                                                                               |

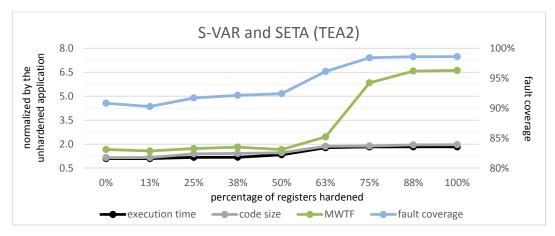

| Fig. 6.18: Results for the TETRA encryption algorithm (TEA2) hardened by S-VAR and SETA. The                                                             |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault                                                  |

| coverage is presented in percentage (right axis)                                                                                                         |

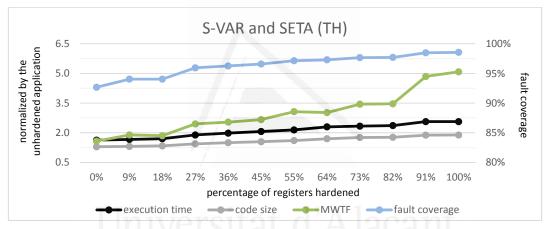

| Fig. 6.19: Results for the Tower of Hanoi (TH) hardened by S-VAR and SETA. The execution time, code                                                      |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                           |

| presented in percentage (right axis)114                                                                                                                  |

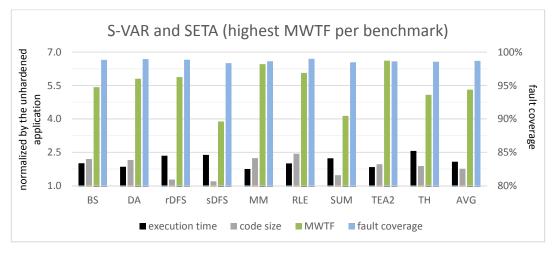

| Fig. 6.20: Highest MWTF for the benchmarks hardened by S-VAR and SETA. The execution time, code         |

|---------------------------------------------------------------------------------------------------------|

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is          |

| presented in percentage (right axis)                                                                    |

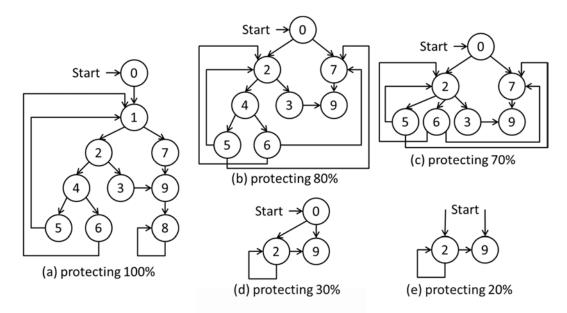

| Fig. 6.21: Example of tunnel effect (S-SETA) (a) protecting 100% of BBs, equivalent to SETA, (b)        |

| protecting 80%, (c) protecting 70%, (d) protecting 30%, and (e) protecting 20% of BBs                   |

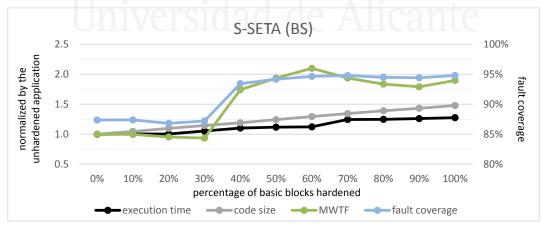

| Fig. 6.22: Results for the bubble sort (BS) hardened by the S-SETA technique. The execution time, code  |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is          |

| presented in percentage (right axis)                                                                    |

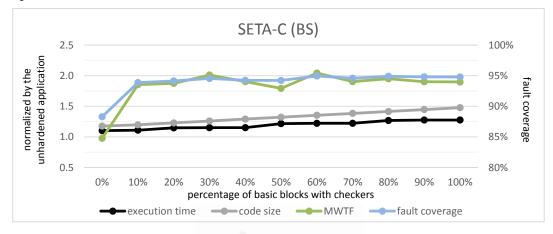

| Fig. 6.23: Results for the bubble sort (BS) hardened by the SETA-C technique. The execution time, code  |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is          |

| presented in percentage (right axis)                                                                    |

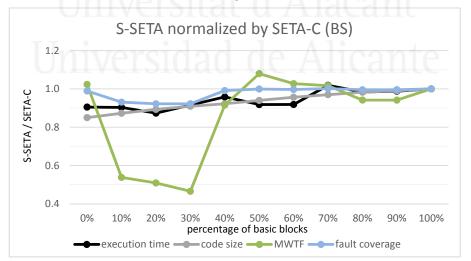

| Fig. 6.24: Comparison between S-SETA and SETA-C for the bubble sort (BS). The results obtained with     |

| S-SETA are normalized by the ones obtained with SETA-C                                                  |

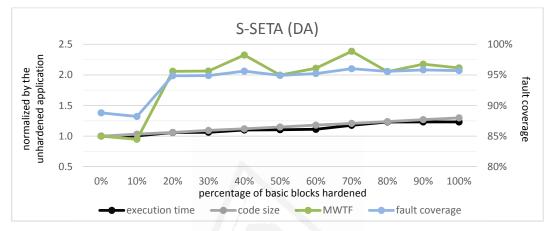

| Fig. 6.25: Results for the Dijkstra's algorithm (DA) hardened by the S-SETA technique. The execution    |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis).                                                                |

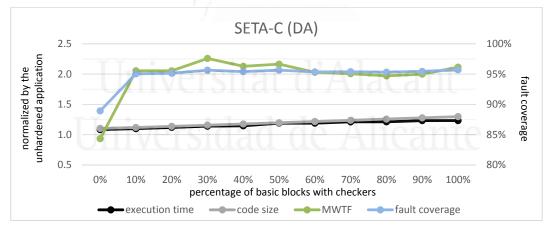

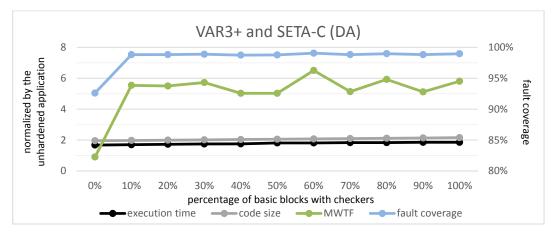

| Fig. 6.26: Results for the Dijkstra's algorithm (DA) hardened by the SETA-C technique. The execution    |

|                                                                                                         |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis)                                                                 |

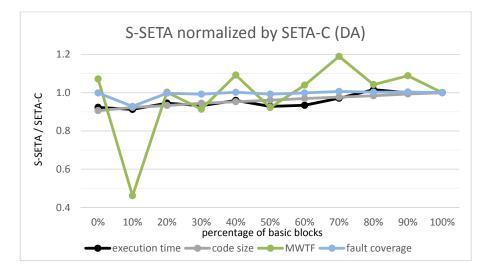

| Fig. 6.27: Comparison between S-SETA and SETA-C for the Dijkstra's algorithm (DA). The results          |

| obtained with S-SETA are normalized by the ones obtained with SETA-C                                    |

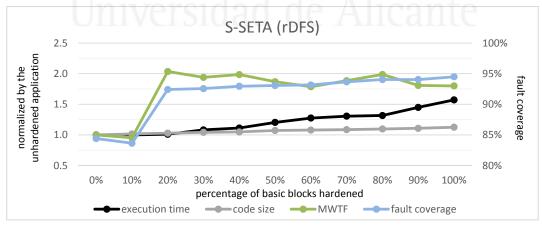

| Fig. 6.28: Results for the recursive depth-first search (rDFS) hardened by the S-SETA technique. The    |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis)                                                        |

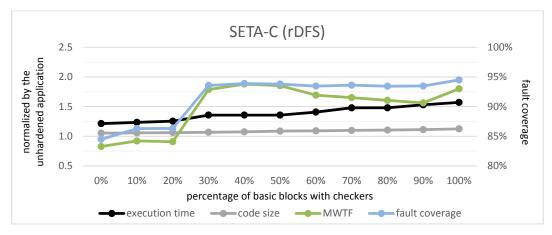

| Fig. 6.29: Results for the recursive depth-first search (rDFS) hardened by the SETA-C technique. The    |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis)                                                        |

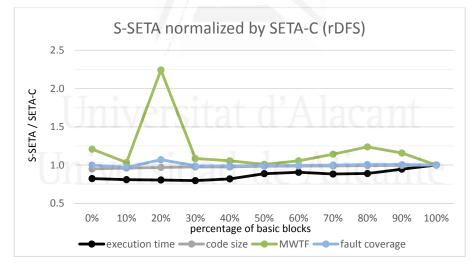

| Fig. 6.30: Comparison between S-SETA and SETA-C for the recursive depth-first search (rDFS). The        |

| results obtained with S-SETA are normalized by the ones obtained with SETA-C                            |

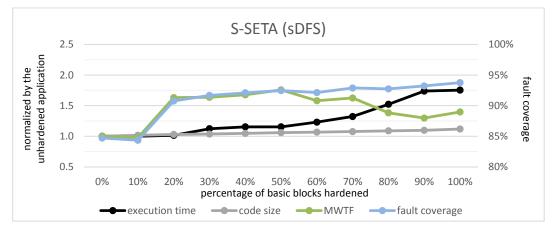

| Fig. 6.31: Results for the sequential depth-first search (sDFS) hardened by the S-SETA technique. The   |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis).                                                       |

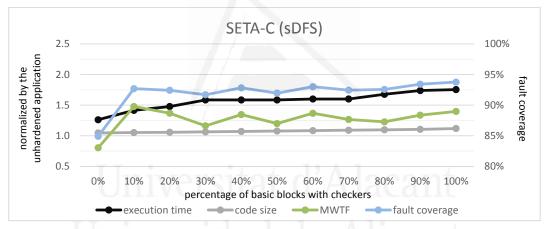

| Fig. 6.32: Results for the sequential depth-first search (sDFS) hardened by the SETA-C technique. The   |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis).                                                       |

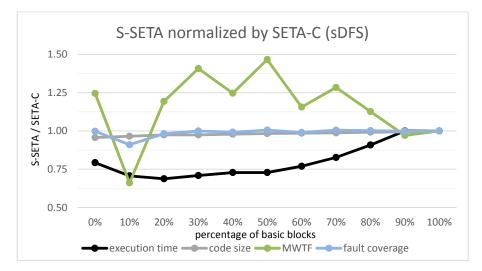

| Fig. 6.33: Comparison between S-SETA and SETA-C for the sequential depth-first search (sDFS). The       |

| results obtained with S-SETA are normalized by the ones obtained with SETA-C                            |

|                                                                                                         |

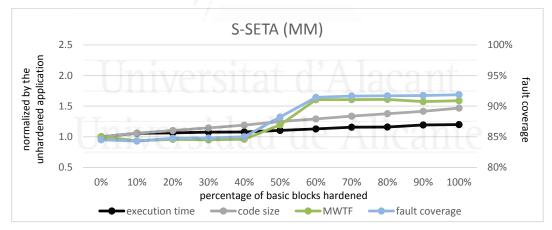

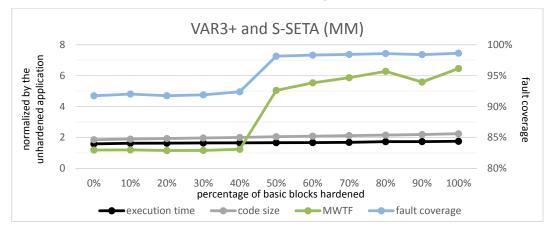

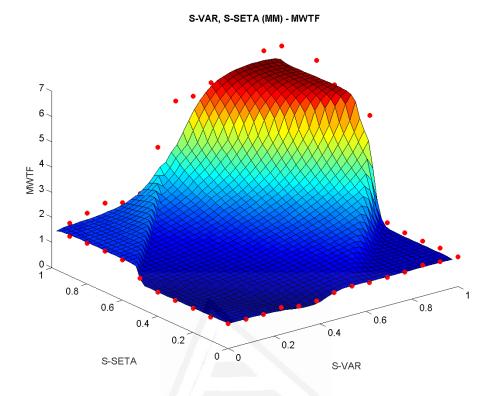

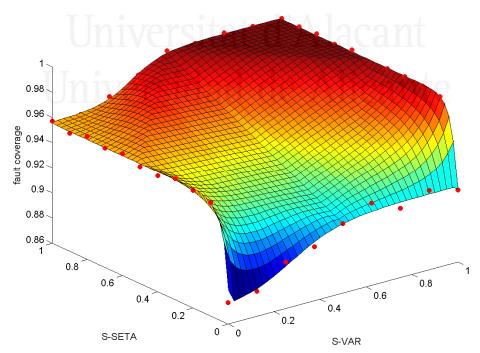

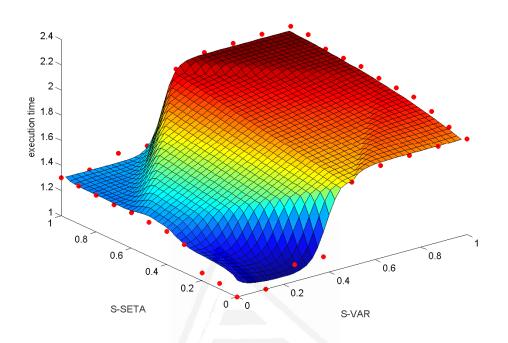

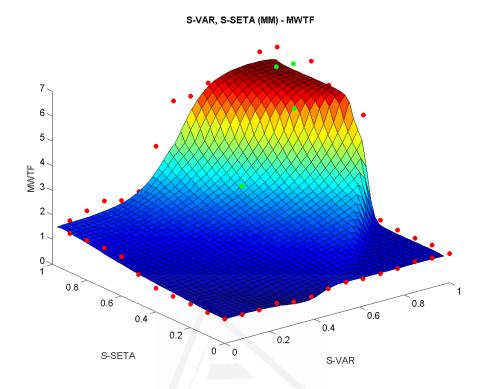

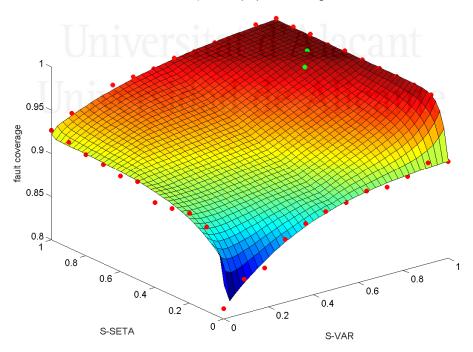

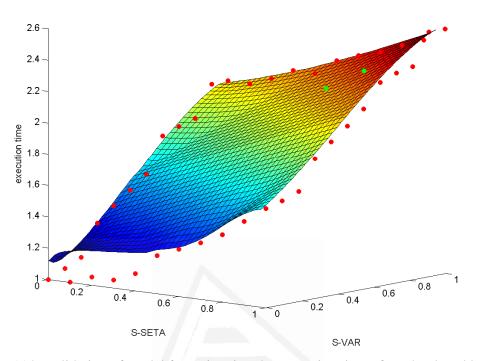

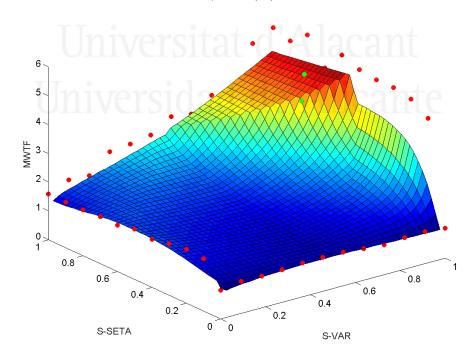

| Fig. 6.34: Results for the matrix multiplication (MM) hardened by the S-SETA technique. The execution   |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis)                                                                 |

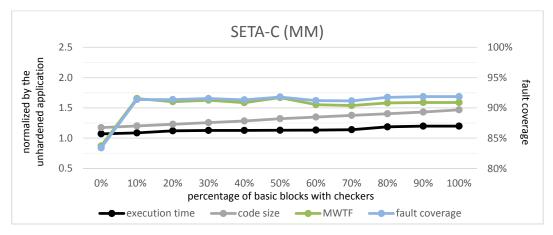

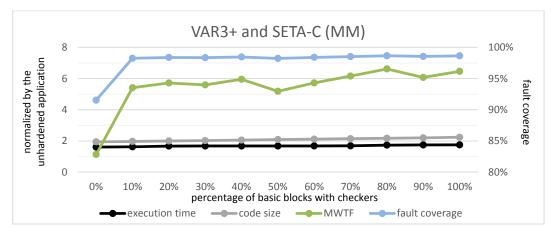

| Fig. 6.35: Results for the matrix multiplication (MM) hardened by the SETA-C technique. The execution   |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis)                                                                 |

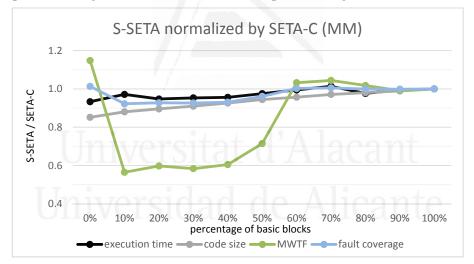

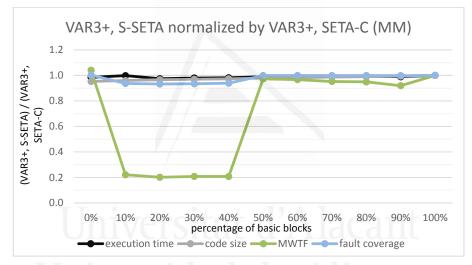

| Fig. 6.36: Comparison between S-SETA and SETA-C for the matrix multiplication (MM). The results         |

| obtained with S-SETA are normalized by the ones obtained with SETA-C                                    |

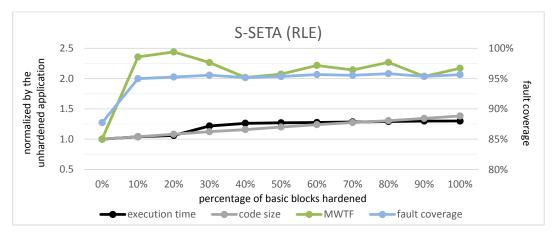

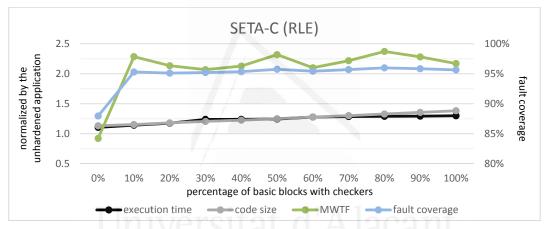

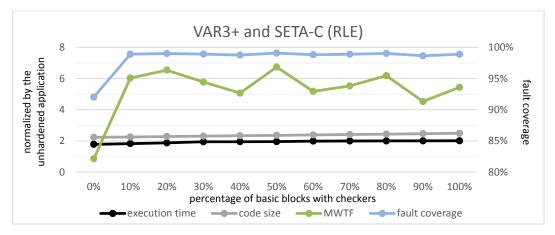

| Fig. 6.37: Results for the run length encoding (RLE) hardened by the S-SETA technique. The execution    |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis)                                                                 |

| Fig. 6.38: Results for the run length encoding (RLE) hardened by the SETA-C technique. The execution    |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis).                                                                |

| Fig. 6.39: Comparison between S-SETA and SETA-C for the run length encoding (RLE). The results          |

| obtained with S-SETA are normalized by the ones obtained with SETA-C                                    |

|                                                                                                         |

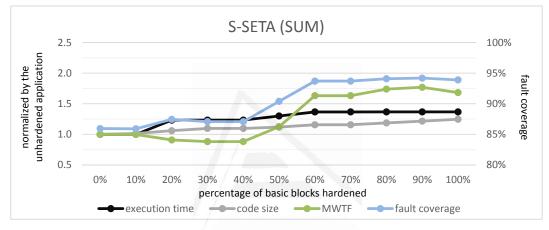

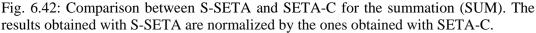

| Fig. 6.40: Results for the summation (SUM) hardened by the S-SETA technique. The execution time, code   |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is          |

| presented in percentage (right axis)                                                                    |

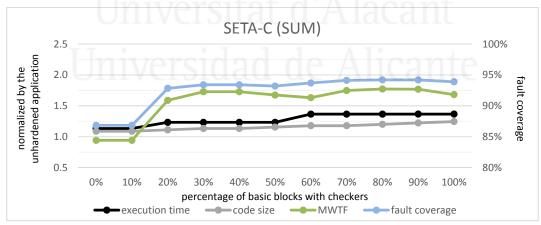

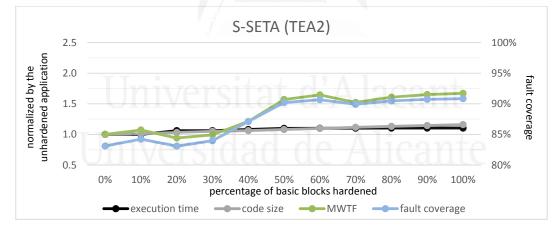

| Fig. 6.41: Results for the summation (SUM) hardened by the SETA-C technique. The execution time, code   |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is          |

| presented in percentage (right axis)126                                                                 |

|                                                                                                         |

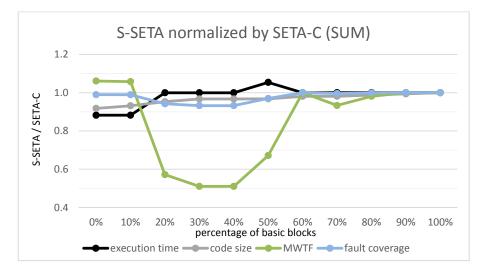

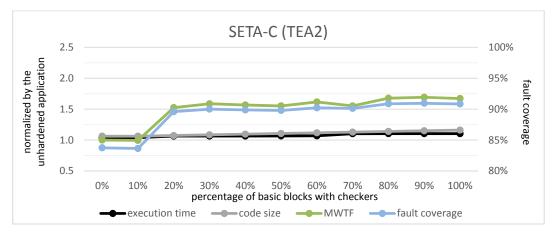

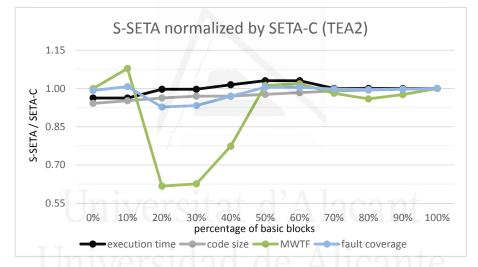

| Fig. 6.42: Comparison between S-SETA and SETA-C for the summation (SUM). The results obtained with      |

|---------------------------------------------------------------------------------------------------------|

| S-SETA are normalized by the ones obtained with SETA-C127                                               |

| Fig. 6.43: Results for the TETRA encryption algorithm (TEA2) hardened by the S-SETA technique. The      |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis)                                                        |

| Fig. 6.44: Results for the TETRA encryption algorithm (TEA2) hardened by the SETA-C technique. The      |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis)                                                        |

| Fig. 6.45: Comparison between S-SETA and SETA-C for the TETRA encryption algorithm (TEA2). The          |

| results obtained with S-SETA are normalized by the ones obtained with SETA-C                            |

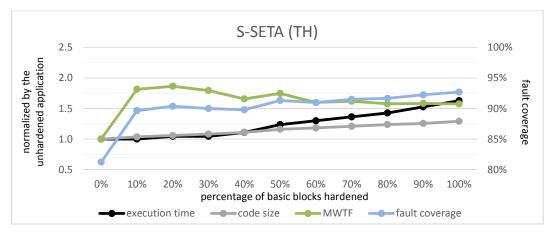

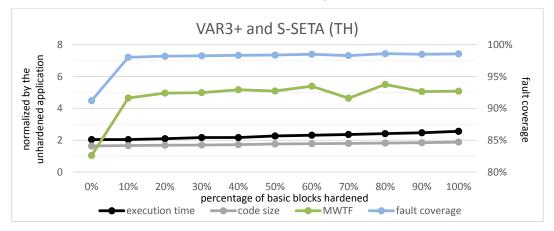

| Fig. 6.46: Results for the Tower of Hanoi (TH) hardened by the S-SETA technique. The execution time,    |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is     |

| presented in percentage (right axis)                                                                    |

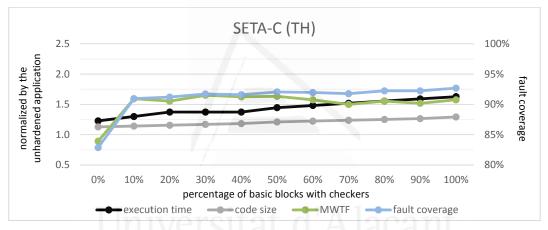

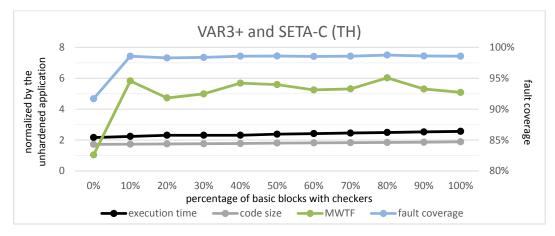

| Fig. 6.47: Results for the Tower of Hanoi (TH) hardened by the SETA-C technique. The execution time,    |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is     |

| presented in percentage (right axis)                                                                    |

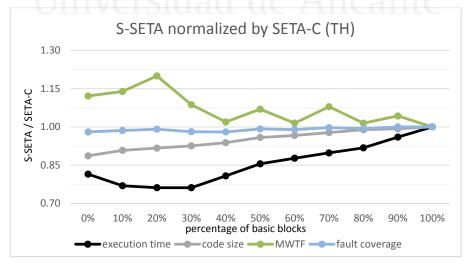

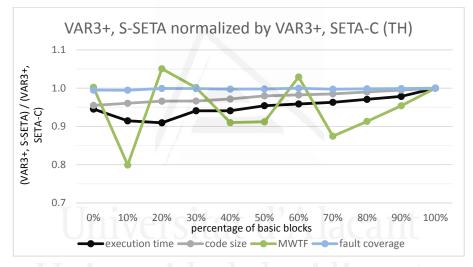

| Fig. 6.48: Comparison between S-SETA and SETA-C for the Tower of Hanoi (TH). The results obtained       |

|                                                                                                         |

| with S-SETA are normalized by the ones obtained with SETA-C                                             |

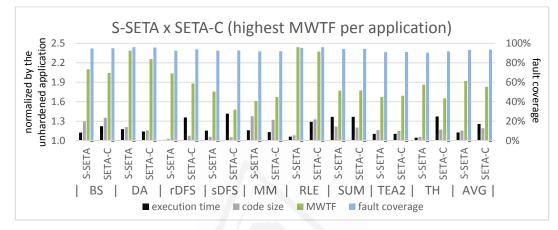

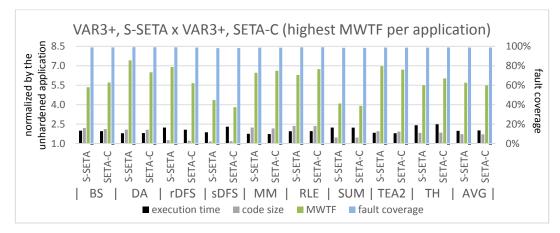

| Fig. 6.49: Highest MWTF for the benchmarks hardened by the S-SETA or SETA-C. The execution time,        |

| code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is     |

| presented in percentage (right axis)                                                                    |

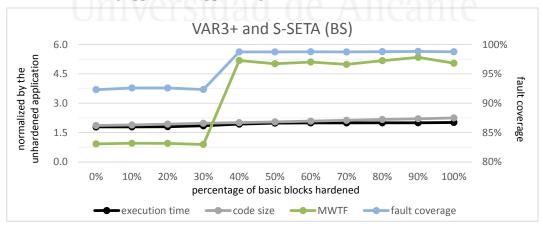

| Fig. 6.50: Results for the bubble sort (BS) hardened by VAR3+ and S-SETA. The execution time, code      |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is          |

| presented in percentage (right axis)130                                                                 |

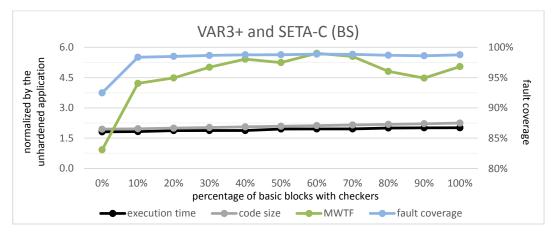

| Fig. 6.51: Results for the bubble sort (BS) hardened by VAR3+ and SETA-C. The execution time, code      |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is          |

| presented in percentage (right axis)                                                                    |

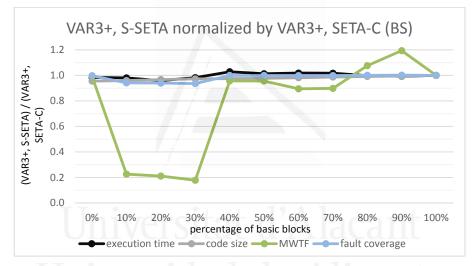

| Fig. 6.52: Comparison between (VAR3+, S-SETA) and (VAR3+, SETA-C) for the BS. The results               |

| obtained with S-SETA are normalized by the ones obtained with SETA-C                                    |

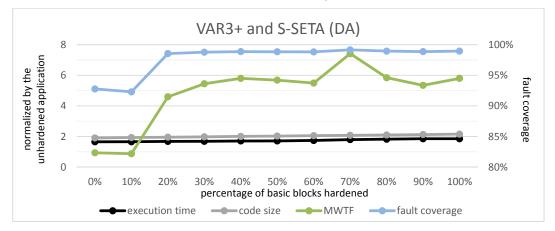

| Fig. 6.53: Results for the Dijkstra's algorithm (DA) hardened by VAR3+ and S-SETA. The execution        |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis)                                                                 |

| Fig. 6.54: Results for the Dijkstra's algorithm (DA) hardened by VAR3+ and SETA-C. The execution        |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis)                                                                 |

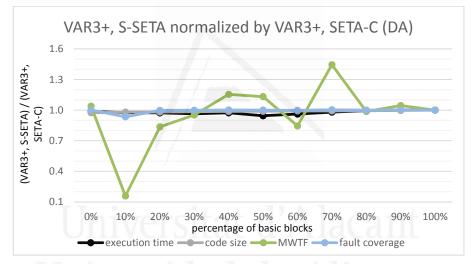

| Fig. 6.55: Comparison between (VAR3+, S-SETA) and (VAR3+, SETA-C) for the DA. The results               |

| obtained with S-SETA are normalized by the ones obtained with SETA-C                                    |

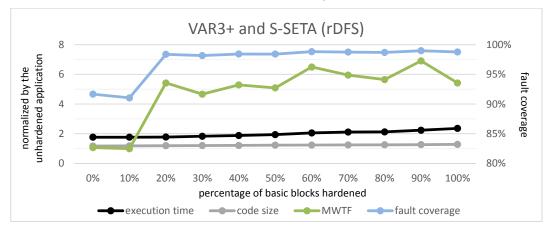

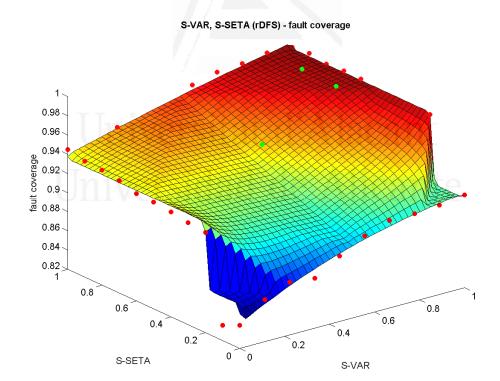

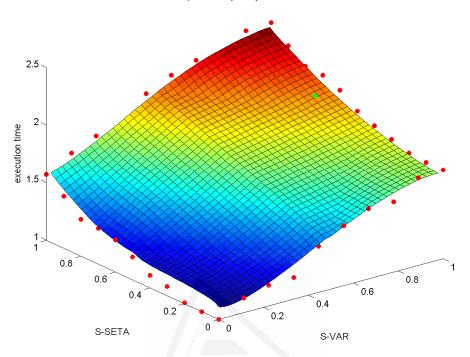

| Fig. 6.56: Results for the recursive depth-first search (rDFS) hardened by VAR3+ and S-SETA. The        |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis)                                                        |

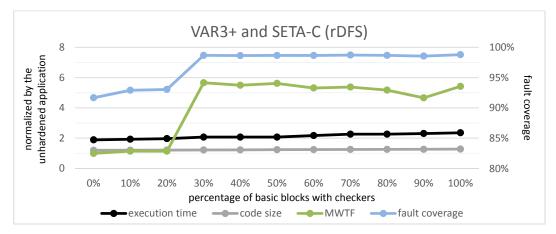

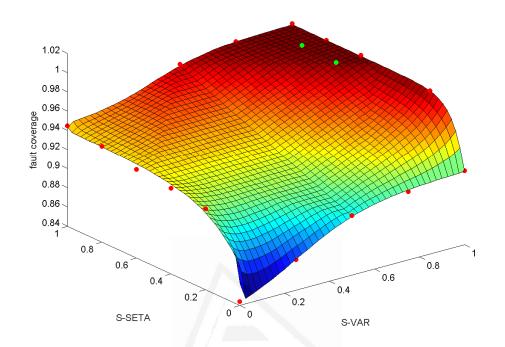

| Fig. 6.57: Results for the recursive depth-first search (rDFS) hardened by VAR3+ and SETA-C. The        |

| Fig. 0.57. Results for the recursive depin-first search (TDFS) hardened by VARS+ and SETA-C. The        |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| <i>coverage is presented in percentage (right axis).</i> 133                                            |

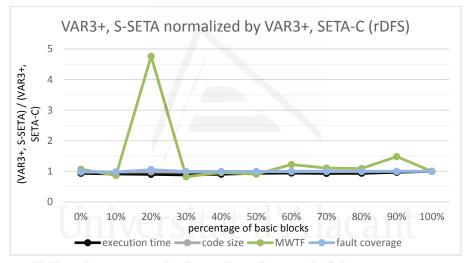

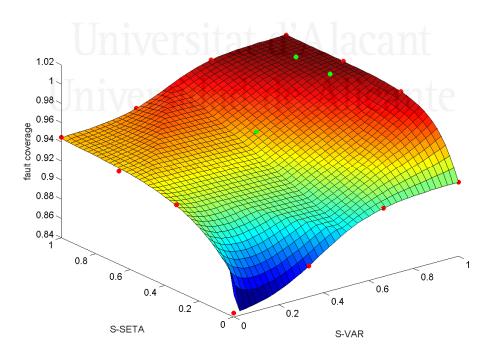

| Fig. 6.58: Comparison between (VAR3+, S-SETA) and (VAR3+, SETA-C) for the rDFS. The results             |

| obtained with S-SETA are normalized by the ones obtained with SETA-C                                    |

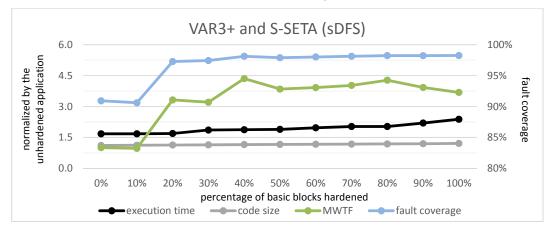

| Fig. 6.59: Results for the sequential depth-first search (sDFS) hardened by VAR3+ and S-SETA. The       |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis)                                                        |

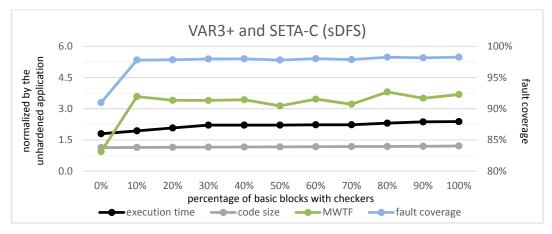

| Fig. 6.60: Results for the sequential depth-first search (sDFS) hardened by VAR3+ and SETA-C. The       |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fault |

| coverage is presented in percentage (right axis)                                                        |

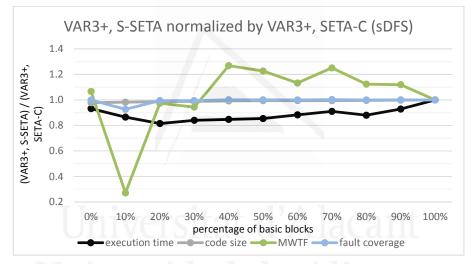

| Fig. 6.61: Comparison between (VAR3+, S-SETA) and (VAR3+, SETA-C) for the sDFS. The results             |

| obtained with S-SETA are normalized by the ones obtained with SETA-C                                    |

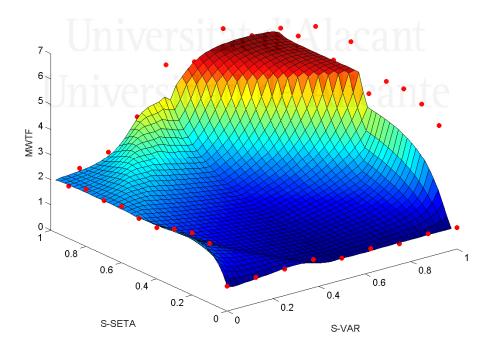

| Fig. 6.62: Results for the matrix multiplication (MM) hardened by VAR3+ and S-SETA. The execution       |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis)                                                                 |

| Fig. 6.63: Results for the matrix multiplication (MM) hardened by VAR3+ and SETA-C. The execution       |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage  |

| is presented in percentage (right axis)                                                                 |

| i i 0 ( 0 /                                                                                             |

| Fig. 6.64: Comparison between (VAR3+, S-SETA) and (VAR3+, SETA-C) for the MM. The results                                                                            |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| obtained with S-SETA are normalized by the ones obtained with SETA-C                                                                                                 | 135  |

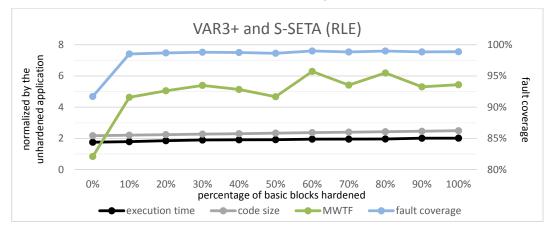

| Fig. 6.65: Results for the run length encoding (RLE) hardened by VAR3+ and S-SETA. The execution                                                                     |      |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage                                                               | зe   |

| is presented in percentage (right axis)                                                                                                                              | 135  |

| Fig. 6.66: Results for the run length encoding (RLE) hardened by VAR3+ and SETA-C. The execution                                                                     |      |

| time, code size, and MWTF are normalized by the unhardened application (left axis). The fault coverage                                                               | ze   |

| is presented in percentage (right axis).                                                                                                                             |      |

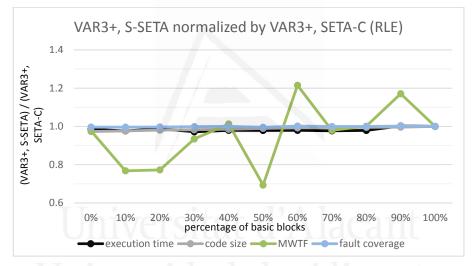

| Fig. 6.67: Comparison between (VAR3+, S-SETA) and (VAR3+, SETA-C) for the RLE. The results                                                                           |      |

| obtained with S-SETA are normalized by the ones obtained with SETA-C.                                                                                                | 136  |

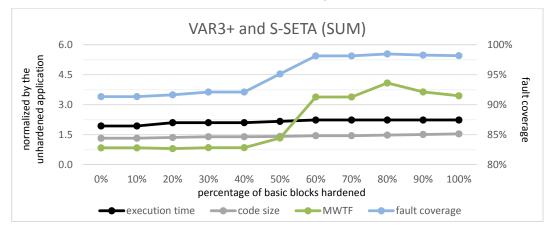

| Fig. 6.68: Results for the summation (SUM) hardened by VAR3+ and S-SETA. The execution time, cod                                                                     |      |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                                       | -    |

| presented in percentage (right axis).                                                                                                                                | 136  |

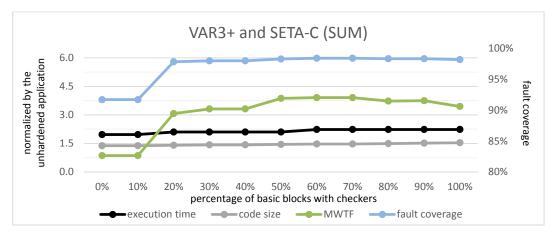

| Fig. 6.69: Results for the summation (SUM) hardened by VAR3+ and SETA-C. The execution time, coc                                                                     |      |

| size, and MWTF are normalized by the unhardened application (left axis). The fault coverage is                                                                       | ic   |

| presented in percentage (right axis).                                                                                                                                | 137  |

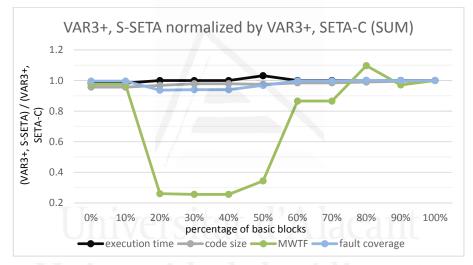

| Fig. 6.70: Comparison between (VAR3+, S-SETA) and (VAR3+, SETA-C) for the SUM. The results                                                                           | 1.57 |

| obtained with S-SETA are normalized by the ones obtained with SETA-C.                                                                                                | 137  |

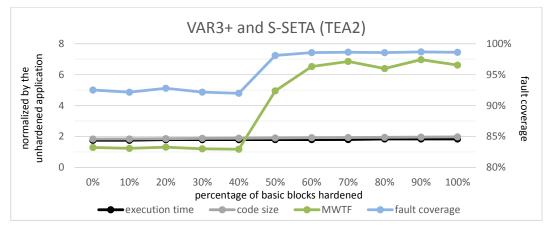

| Fig. 6.71: Results for the TETRA encryption algorithm (TEA2) hardened by VAR3+ and S-SETA. The                                                                       | 157  |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fai                                                                | 1+   |

| coverage is presented in percentage (right axis).                                                                                                                    |      |

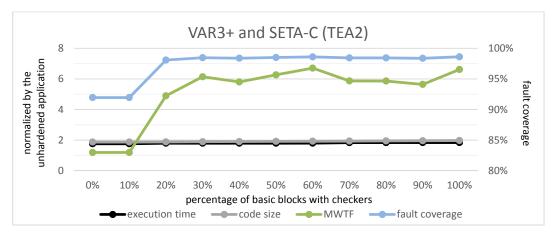

| Fig. 6.72: Results for the TETRA encryption algorithm (TEA2) hardened by VAR3+ and SETA-C. The                                                                       | 157  |

|                                                                                                                                                                      |      |

| execution time, code size, and MWTF are normalized by the unhardened application (left axis). The fai                                                                |      |

| coverage is presented in percentage (right axis).                                                                                                                    | 130  |

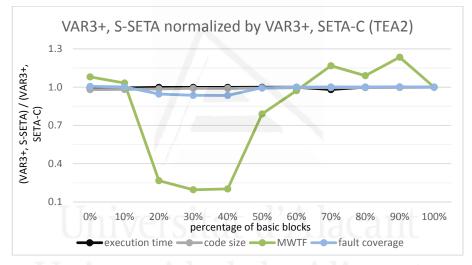

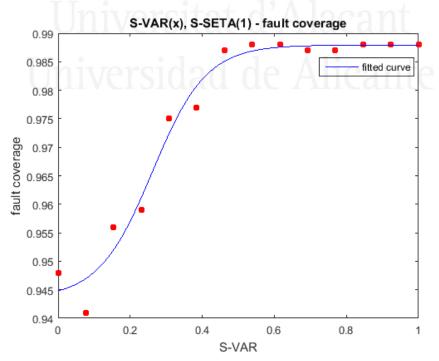

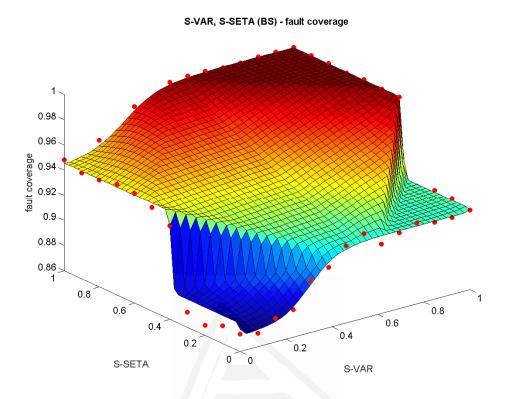

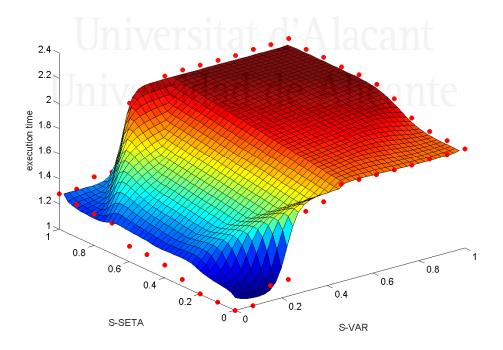

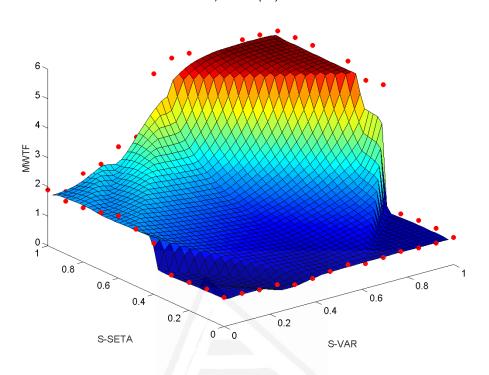

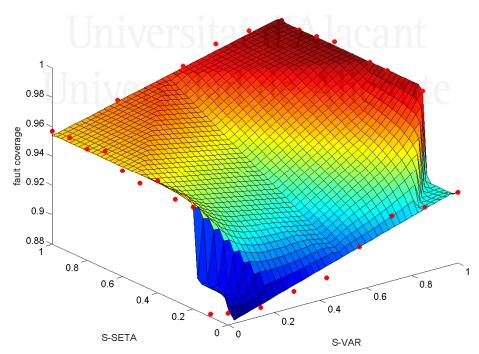

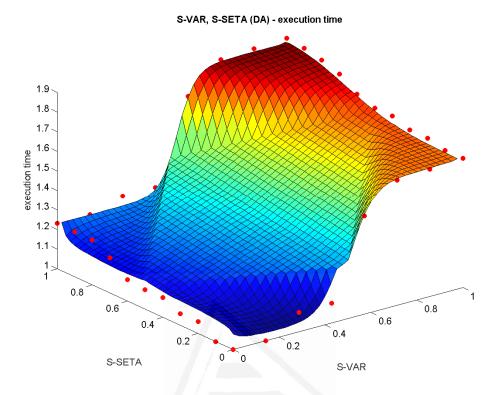

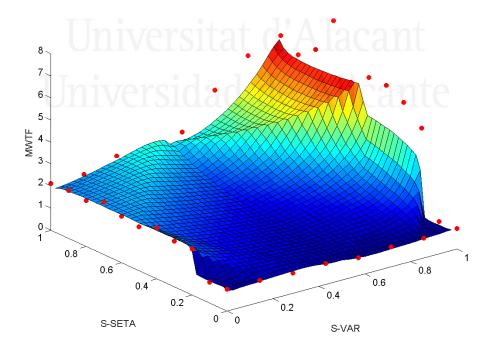

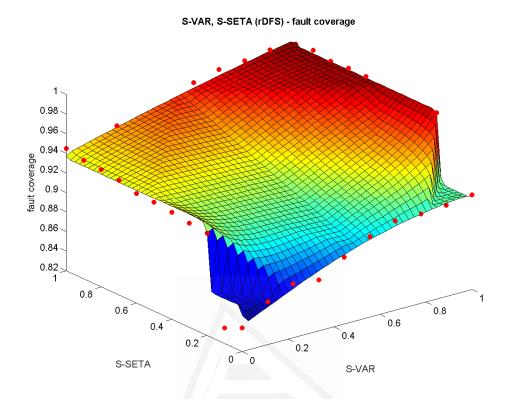

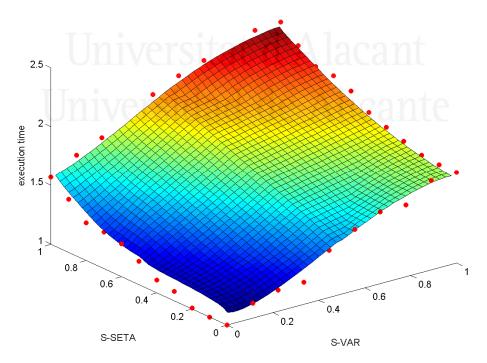

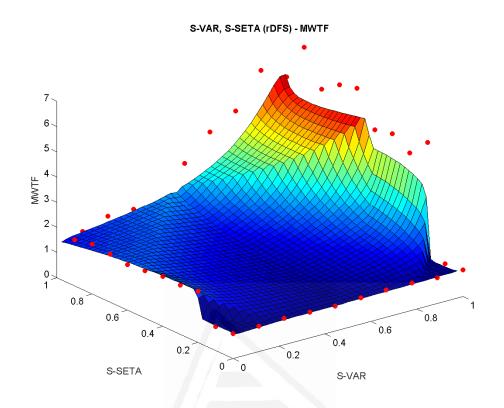

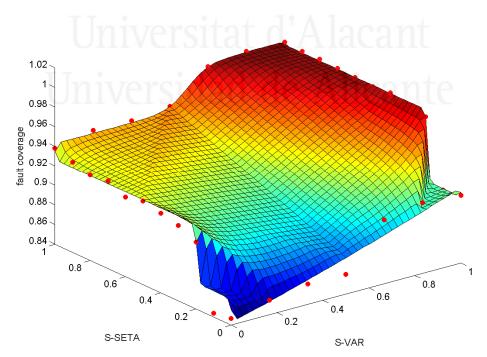

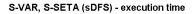

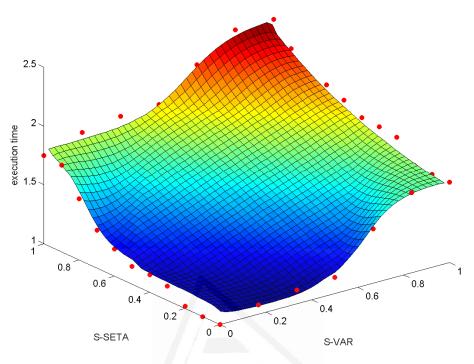

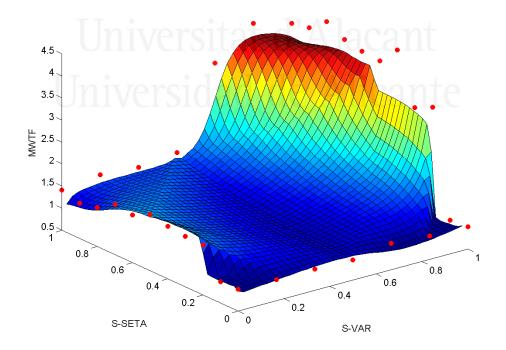

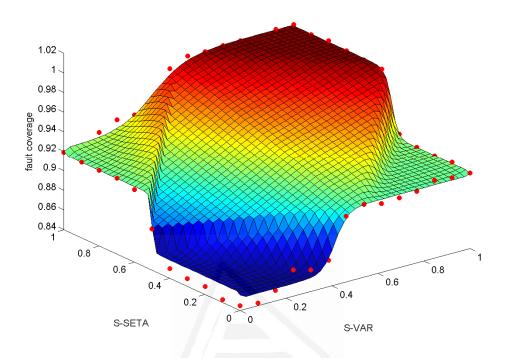

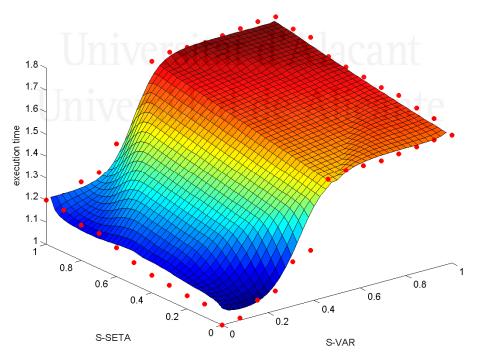

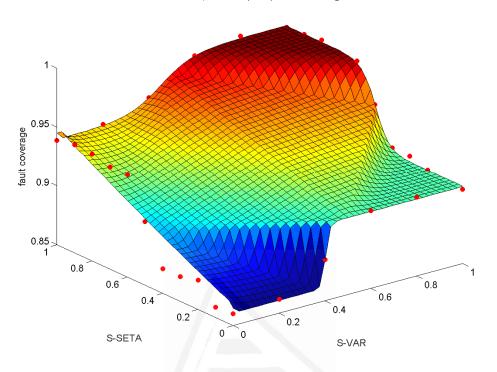

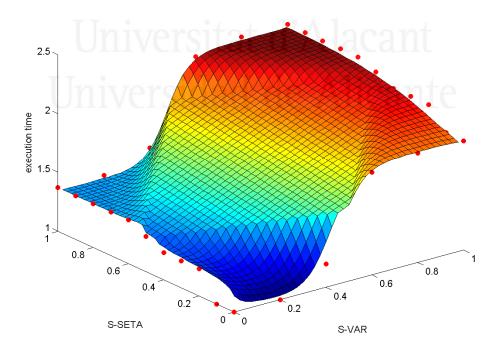

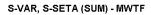

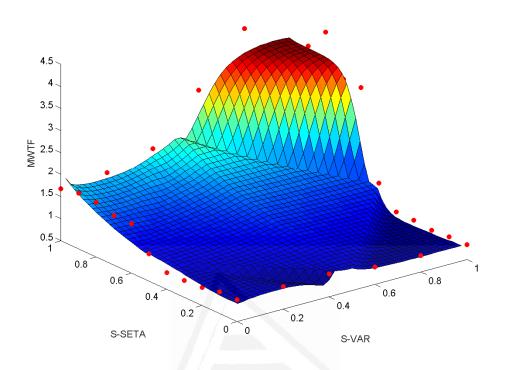

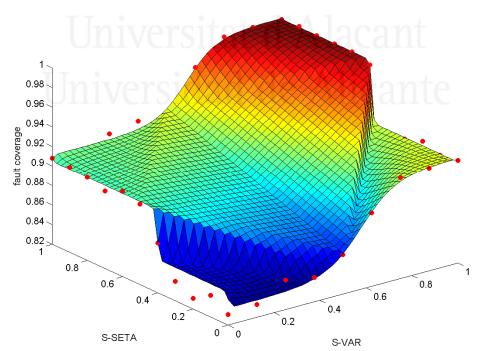

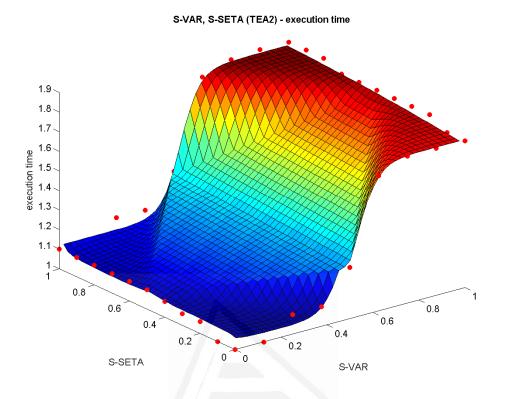

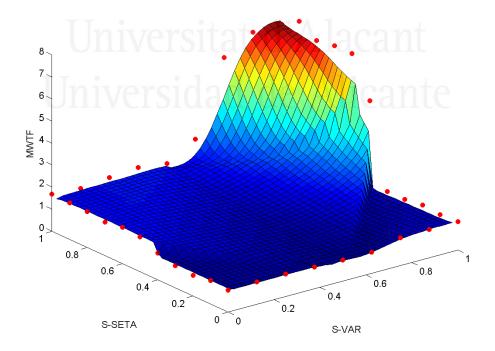

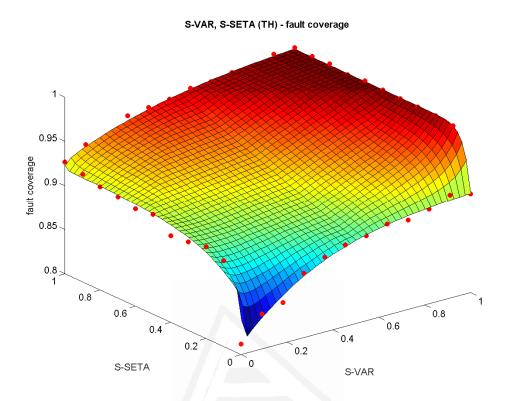

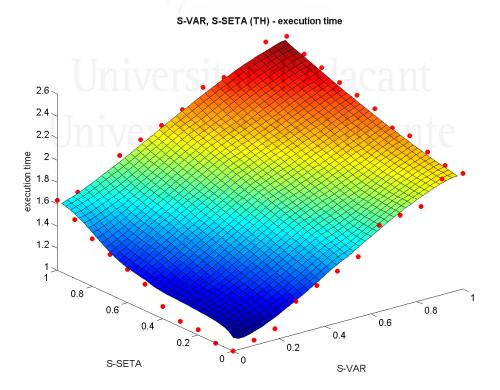

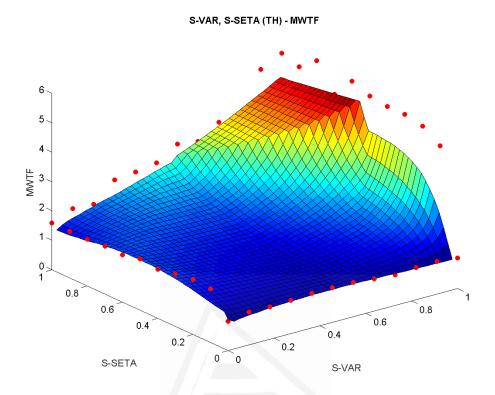

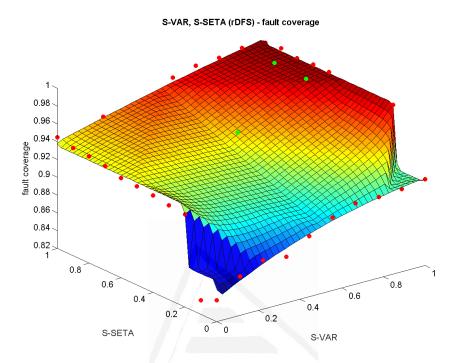

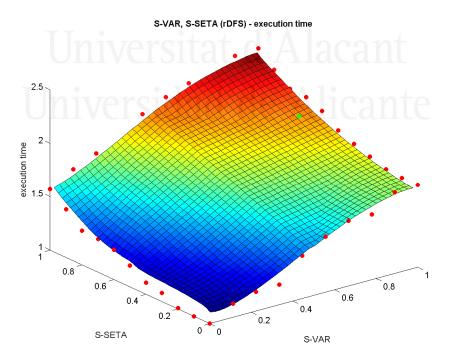

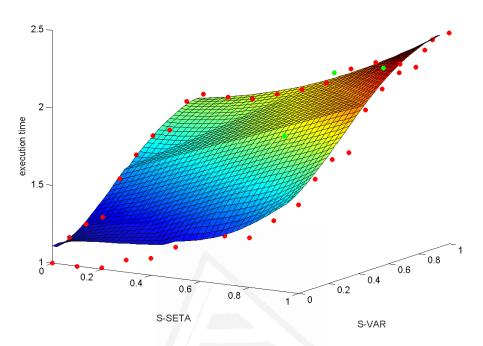

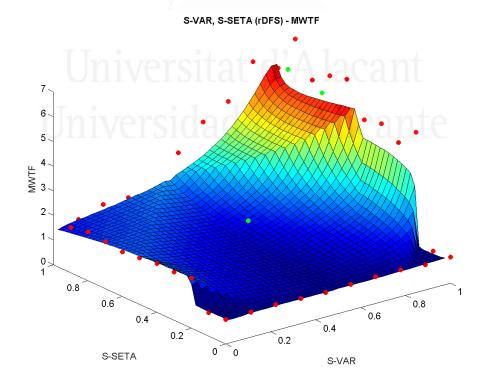

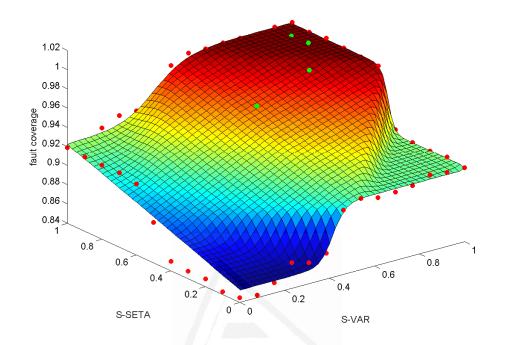

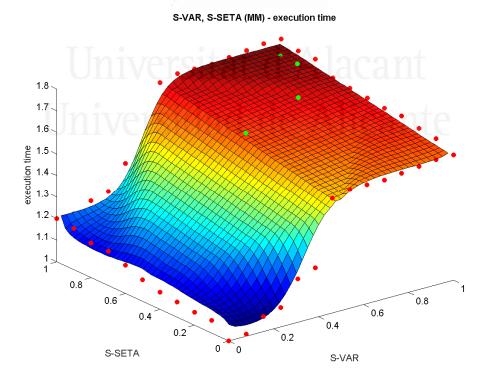

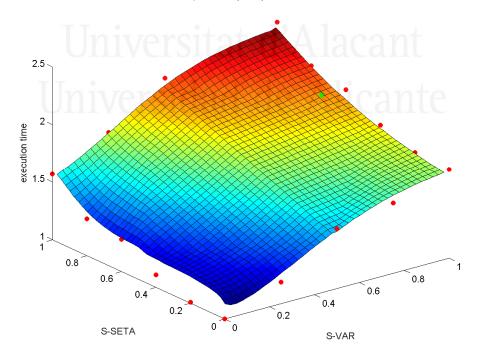

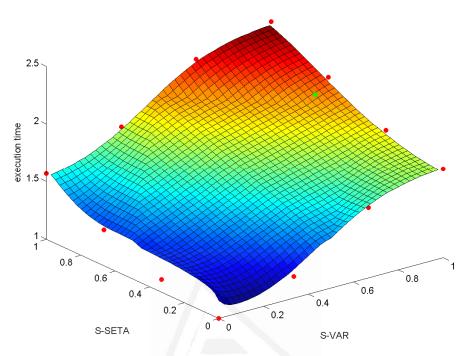

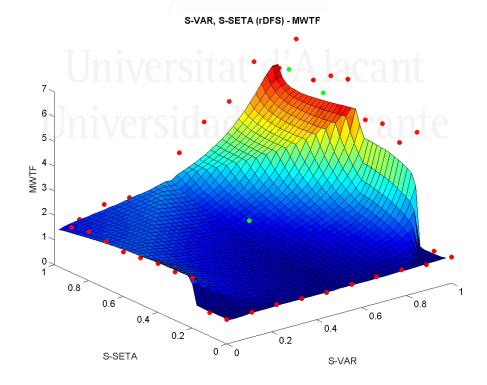

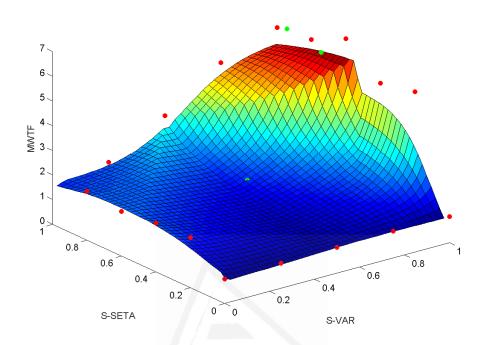

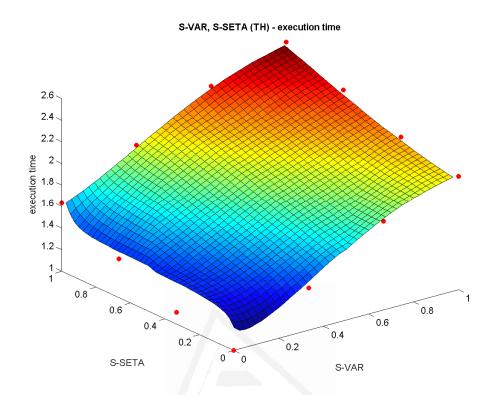

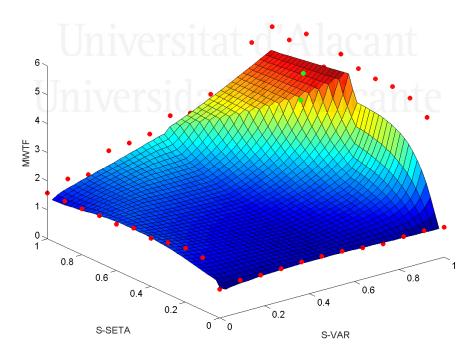

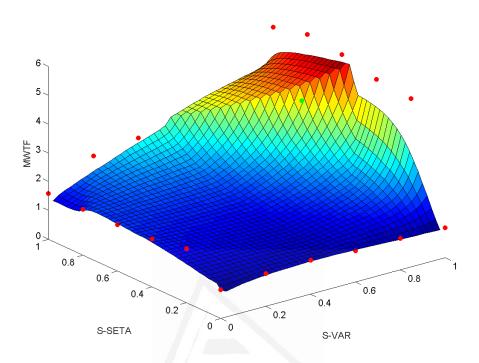

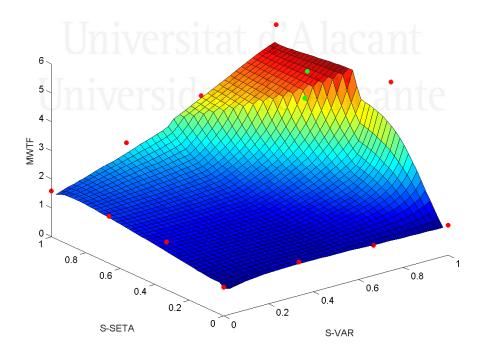

| Fig. 6.73: Comparison between (VAR3+, S-SETA) and (VAR3+, SETA-C) for TEA2. The results obtain                                                                       |      |